Example: MultiChannelDAQ

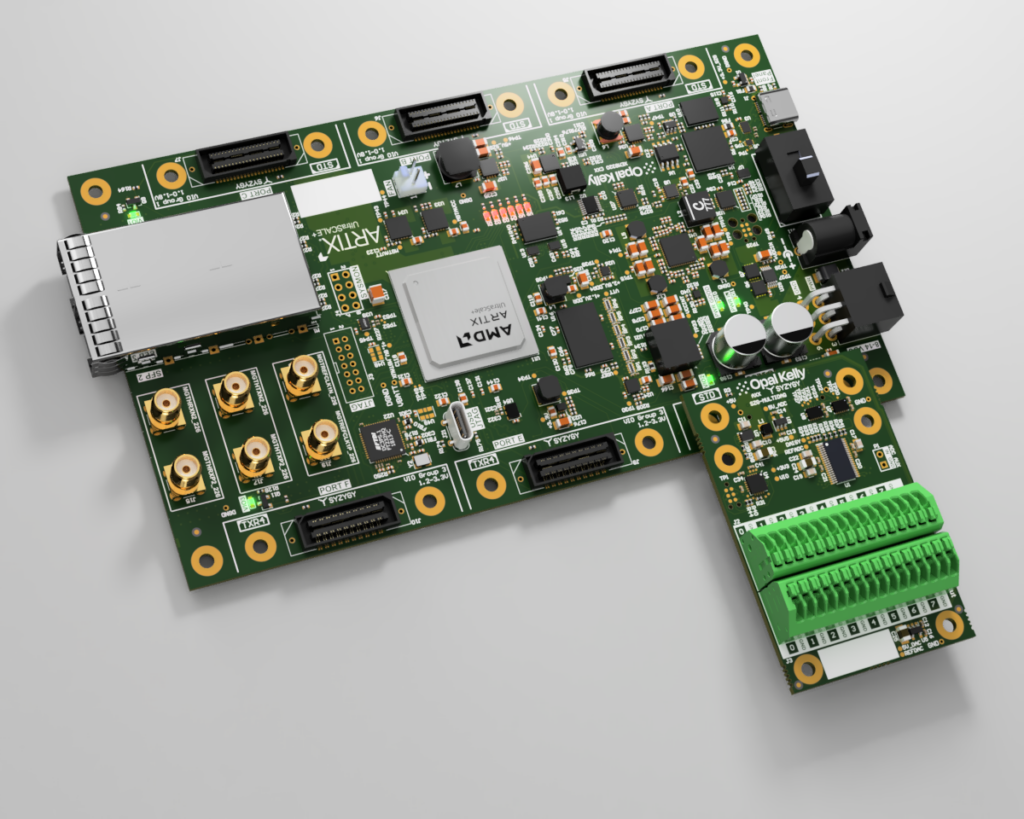

The MultiChannelDAQ example design features a GUI enabled by FrontPanel Platform, allowing users to manage 8 near-real-time DAC and ADC channels. The DAC channels function as a signal generator, producing sinusoidal waves using a CORDIC core, while the ADC channels function as an oscilloscope. The FrontPanel Platform software and gateware control two ADC and DAC controllers to operate the SZG-MULTIDAQ on the XEM8320. With FrontPanel Platform, users have access to open-source JavaScript libraries, and in this example, we utilize Chart.js to provide a versatile toolkit for data acquisition and oscilloscope display, serving as a foundation for more advanced projects.

Resources

Learning Objectives

- Set up and use a GUI enabled by FrontPanel Platform for controlling gateware.

- Utilize the open-source JavaScript library Chart.js for data acquisition and oscilloscope display.

- Interface with the SZG-MULTIDAQ on the XEM8320.

Getting Started

The goal of this getting started guide is to run the provided example design using prebuilt sources. This is a crucial first step to ensure correct hardware setup with known good sources.

Requirements

- Latest MultiChannelDAQ-ExampleDesign-vX.Y release ASAR file

- The FPGA bitfile is contained in this file. The ASAR is all you need!

- FrontPanel 6.0.0 beta or higher

- XEM8320-AU25P

- SZG-MULTIDAQ on Port D of the XEM8320

Running the Example Design

Hardware Setup

- Connect Devices: Connect the XEM8320 and the SZG-MULTIDAQ, then power them on.

- Add Physical Connection: Connect Channel 1 of the DAC to Channel 1 of the ADC using a piece of conductive wire.

FrontPanel Platform Application Setup

- Open the FrontPanel Platform application.

- Install the MultiChannelDAQ application by clicking the ‘+’ button in the Application Card panel. Then locate the

MultiChannelDAQ-ExampleDesign-vX.Y.asarfile you downloaded from the latest MultiChannelDAQ-ExampleDesign-vX.Y release. See: Building the Template App Guide for more details. - Connect an XEM8320 device to your PC.

- Click and drag the MultiChannelDAQ Application card to the available XEM8320 device.

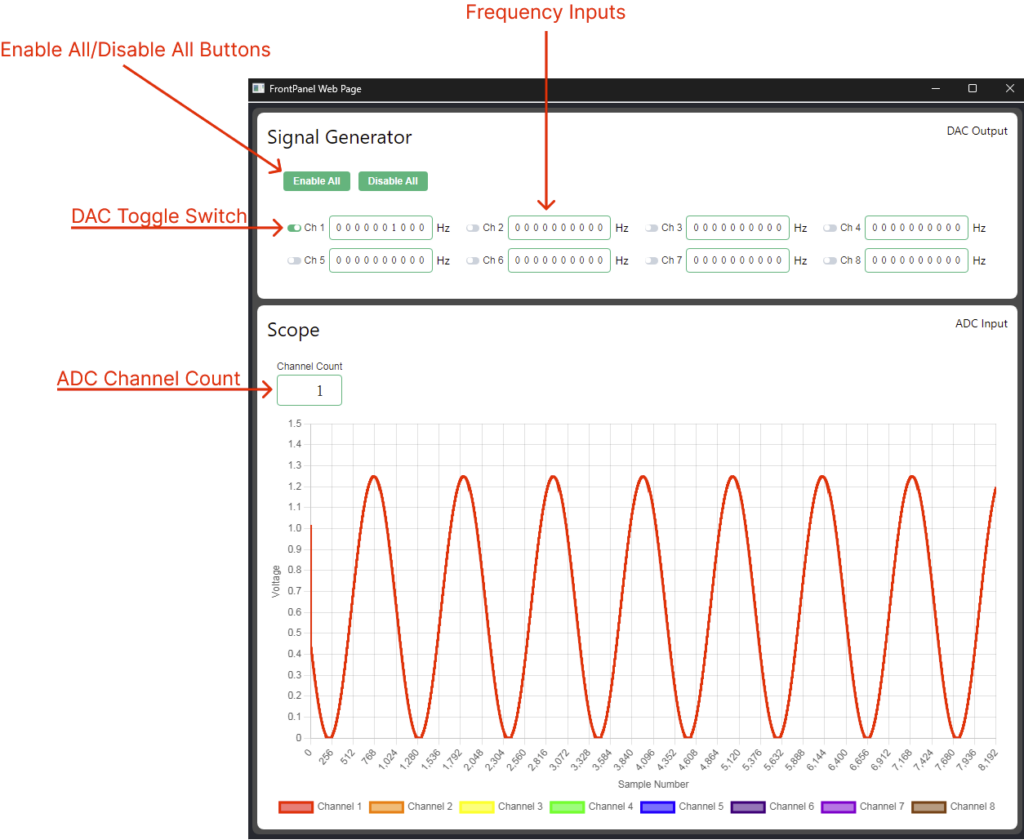

Example Design Application Setup

- Enable Channel 1 of the DAC: Set the frequency to 1000 using the number entry component.

- Enable Channel 1 of the ADC: The graph will display the retrieved data from the ADC in red.

How-To Build the Gateware

Requirements

- Latest MultiChannelDAQ-ExampleDesign-vX.Y release Source Code (zip or tar.gz)

- Vivado

Notice: Our tested version is v2023.2. Versions outside of this are not guaranteed to work. - FrontPanel Vivado IP Core v1.0.5 or higher

Building the Gateware

- Extract Example Design Release: Unzip/tar.gz the Example Design release and note the location for step 3.

- Add IP Cores to Vivado: Follow the instructions for Vivado IP Cores’ Distribution v1.0.5 or later and note the installation location for step 4.

- Navigate to Gateware Folder: Open the Vivado GUI and navigate to the MultiChannelDAQ gateware folder using the TCL Console.

- Example:

cd C:/path/to/MultiChannelDAQ/Gateware

- Example:

- Set IP Core Path: Set the fpdir variable to the IP core path.

- Example:

set fpdir C:/path/to/FrontPanel-Vivado-IP-Dist-vX.Y.Z

- Example:

- Run Setup Script: Run source project.tcl.

- Generate Bitstream: Click ‘Generate Bitstream’ once the project is ready.

How-To Build the Software

Requirements

- Latest MultiChannelDAQ-ExampleDesign-vX.Y release Source Code (zip or tar.gz)

- multidaq.bit

- Install prerequisites from the Building the Template App guide.

- FrontPanel 6.0.0 installed

Build the Software

- Open Folder: Open the

Softwarefolder in Visual Studio Code. This folder is located in the MultiChannelDAQ-ExampleDesign-vX.Y release Source Code. - Add Prebuilt Bitfile: Copy the

multidaq.bitto theassetsfolder. - Install Dependencies: Run

npm installwithin a Visual Studio command terminal. - Build Project: Run

npm run packwithin a Visual Studio command terminal. - Locate Output: The

app.asarfile is located in theoutputfolder. - Start FrontPanel Platform: Open FrontPanel Platform Application.

- Install Application: Install the app.asar by clicking the ‘+’ button in the Installed Applications panel of the FrontPanel Platform. For more details, see Building the Template App Guide.

- Run Application: Click and drag the MultiChannelDAQ Application card to an available XEM8320 device

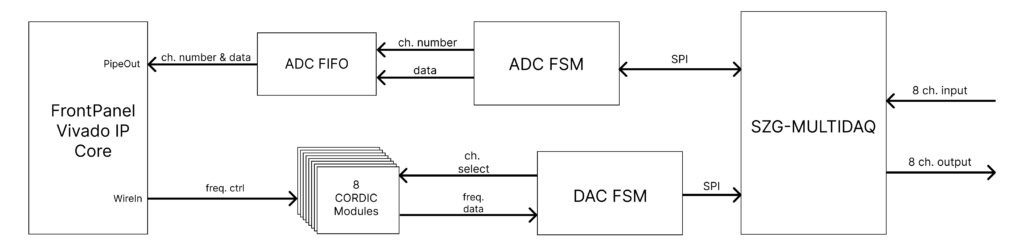

Gateware Architecture Reference

ADC Path

- ADC FSM (Finite State Machine): Manages SPI communication with the SZG-MULTIDAQ to receive digital values for 8 channels.

- ADC FIFO: Stores the digital values in a header-payload format. The header indicates the channel, and the payload contains the data.

- Data Flow: Digital values are gathered from SZG-MULTIDAQ via SPI → ADC FSM → ADC FIFO → FrontPanel Vivado IP Core (PipeOut) → Host Application.

DAC Path

- 8 CORDIC Modules: Generate sinusoidal output for each of the 8 DAC channels. Frequency is controlled by the user application.

- DAC FSM: Stripes through the 8 CORDIC outputs, collecting output data and transmitting it via SPI to the SZG-MULTIDAQ.

- Data Flow: Frequency control data from FrontPanel Vivado IP Core (WireIn) → 8 CORDIC Modules → DAC FSM → SZG-MULTIDAQ (via SPI).

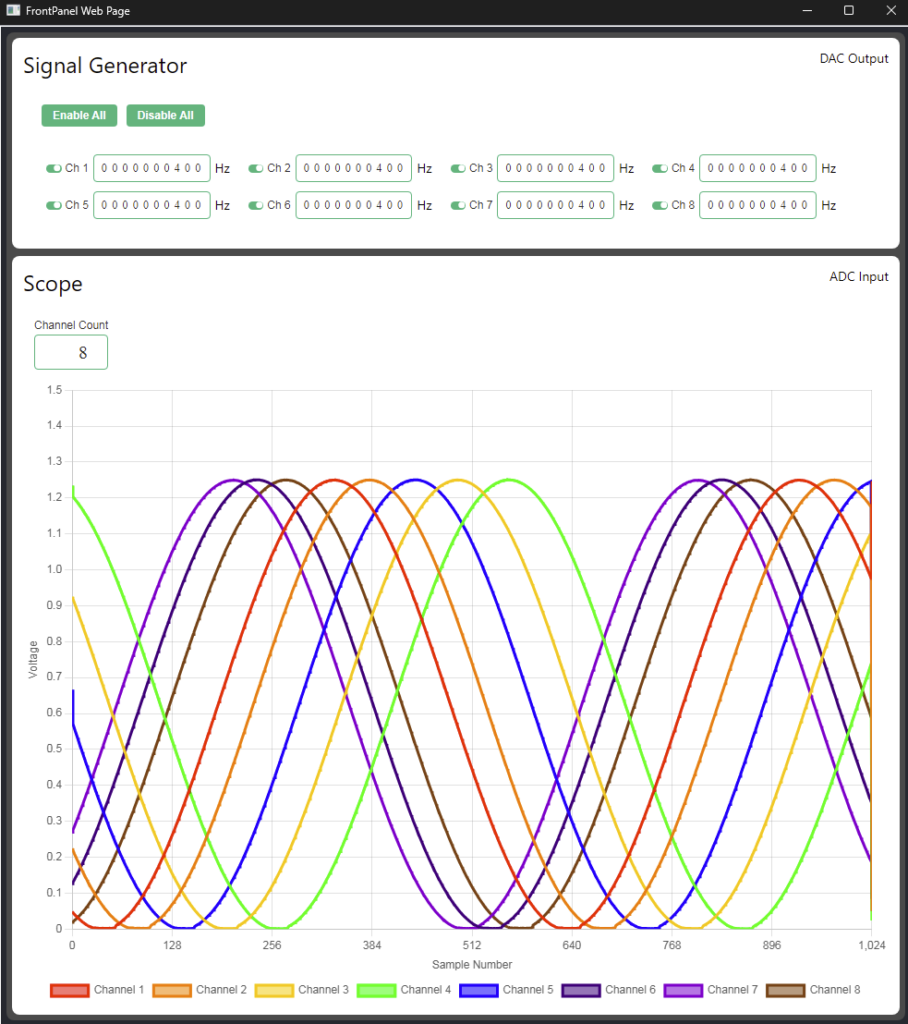

FrontPanel Platform GUI Reference

The user interface shown above has the following components to control the behavior of the SZG-MULTIDAQ:

GUI elements are labeled with a red number corresponding to the key below.

- ADC Channel Count – This selects the number of ADC channels that will be active. The more active channels there are, the slower the effective sampling rate.

- Enable All/Disable All – Enables/Disables all DAC channels.

- DAC Toggle Switches – If untoggled, disables the specific DAC channel.

- Frequency (Hz) – The frequency of the specified DAC Channel.

Release Notes

Our releases for the MultiDAQ Example Design are located on GitHub at:

opalkelly-opensource/MultiChannelDAQ Releases

MultiChannelDAQ Example Design 3.1

- Example renamed and migrated into a separate repository

Previous Versions

MultiDAQ Example Design 3.1

- Updated to provide application information

MultiDAQ Example Design 3.0

- Updated to use version 0.5.0 of the FrontPanel Platform API

- Updated so application can be installed in the FrontPanel Platform launcher

MultiDAQ Example Design 2.0

- Upgrade to utilize FrontPanel Platform

MultiDAQ Example Design 1.0 (Deprecated)

- Initial Creation

- Prebuilt bitfile generated using the following tool versions:

- Vivado v2023.2

- Vivado IP Cores’ Distribution v1.0.5

- Prebuilt Alloy application generated using the following tool versions:

- FP-Alloy Core library v0.1.0

- FrontPanel React component library v0.1.0