Reset Profiles

Reset Profiles (USB 3.0 Only)

Reset Profiles are supported on select USB 3.0 devices. Reset Profiles are not supported on UltraScale or UltraScale+ devices.

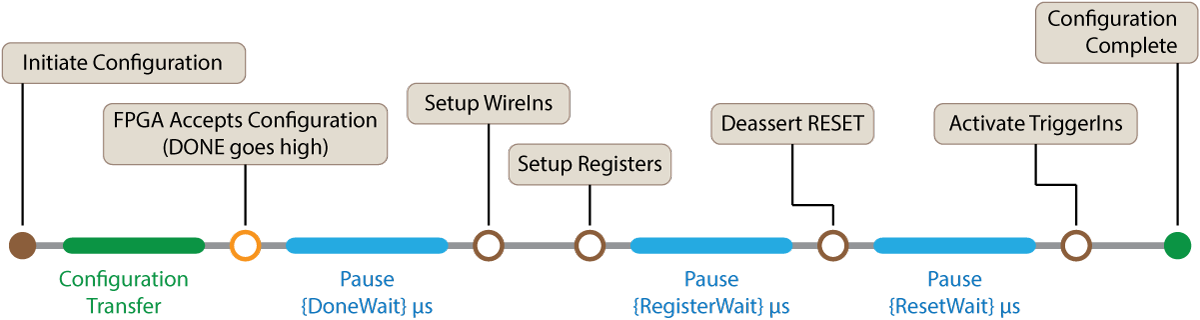

A FrontPanel Reset Profile defines a structured approach to setting up your FPGA design after configuration has completed. The intent is to simplify initialization of your FrontPanel-enabled design by making sure certain inputs (such as WireIns or Registers) are setup prior to deasserting RESET. Including a Reset Profile, the FPGA configuration process includes the steps illustrated below.

- FPGA configuration is initiated, clearing the present configuration memory.

- RESET is asserted (active high).

- Configuration data is transferred to the FPGA.

- Upon valid configuration, the FPGA indicates completion to the firmware. For AMD FPGAs, this corresponds to DONE going high.

- Pause for {DoneWait}, then WireIns are set to predefined values.

- RegisterIns are set to predifined values.

- Pause for {RegisterWait}, then RESET is deasserted.

- Pause for {ResetWait}, then predefined TriggerIns are activated.

- Configuration with Reset is complete.

The reset process is controlled using the Reset Profile defined with the okTFPGAResetProfile structure. FrontPanel API methods that accept a Reset Profile are described in the following table.

| METHOD | DESCRIPTION |

|---|---|

| ConfigureFPGAWithReset | Configure the FPGA from a file and perform a Reset Profile after configuration. |

| ConfigureFPGAFromMemoryWithReset | Configure the FPGA from memory and perform a Reset Profile after configuration |

| GetFPGABootResetProfile | Retrieves the Reset Profile stored in Flash memory that is used for power-on configuration of the FPGA. |

| GetFPGAJTAGResetProfile | Retrieves the Reset Profile stored in Flash memory that is used for JTAG configuration of the FPGA. |

| SetFPGABootResetProfile | Sets the Reset Profile stored in Flash memory that is to be used for power-on configuration of the FPGA. |

| SetFPGAJTAGResetProfile | Sets the Reset Profile stored in Flash memory that is to be used for JTAG configuration of the FPGA. |

typedef struct okFPGAResetRegisterEntry {

UINT32 address;

UINT32 data;

} okTFPGAResetRegisterEntry;

typedef struct okFPGAResetTriggerEntry {

UINT32 address;

UINT32 mask;

} okTFPGAResetTriggerEntry;

typedef struct okFPGAResetProfile {

UINT32 magic;

UINT32 configFileLocation;

UINT32 configFileLength;

UINT32 doneWaitUS;

UINT32 resetWaitUS;

UINT32 registerWaitUS;

UINT32 padBytes1[28];

UINT32 wireInValues[32];

UINT32 registerEntryCount;

okTFPGAResetRegisterEntry registerEntries[256];

UINT32 triggerEntryCount;

okTFPGAResetTriggerEntry triggerEntries[32];

UINT8 padBytes2[1520];

} okTFPGAResetProfile;