BRK8350 Breakout Board

Powering the BRK8350

The BRK8350 requires a clean, filtered, DC supply within the range of 6 V to 16 V. This supply may be delivered in one of two ways:

- 6-pin Mini-Fin connector – Pins 1, 2, and 3 are tied to the input supply net +VDCIN. Pins 4, 5, and 6 are tied to ground. The total maximum current allowed over this connector is 8 A. The part number is Molex 0455580003. The mating plug part number is Molex 0455590002. Several options for crimping pins are available, including Molex 0039000038. While it is possible to provide power using a commercial PC power supply with compatible pinout, it is recommended to create a custom cable harness for use with an appropriate bench supply.

- DC barrel jack – The jack is part number PJ-102AH from CUI, Inc. It is a standard “canon-style” 2.1mm / 5.5mm jack. The outer ring is connected to DGND. The center pin is connected to +VDCIN.

Please refer to Powering the XEM8350 for information on the XEM8350 power systems.

IPMI EEPROM

The XEM8350 may optionally read peripheral information and configuration data from a small EEPROM on the peripheral. If available, the EEPROM can be used to automatically set the voltages for the three programmable voltage regulators on the XEM8350. An EEPROM is installed on the BRK8350 but is not loaded with any configuration. Use Opal Kelly’s IPMI EEPROM Generator Tool to generate an EEPROM image.

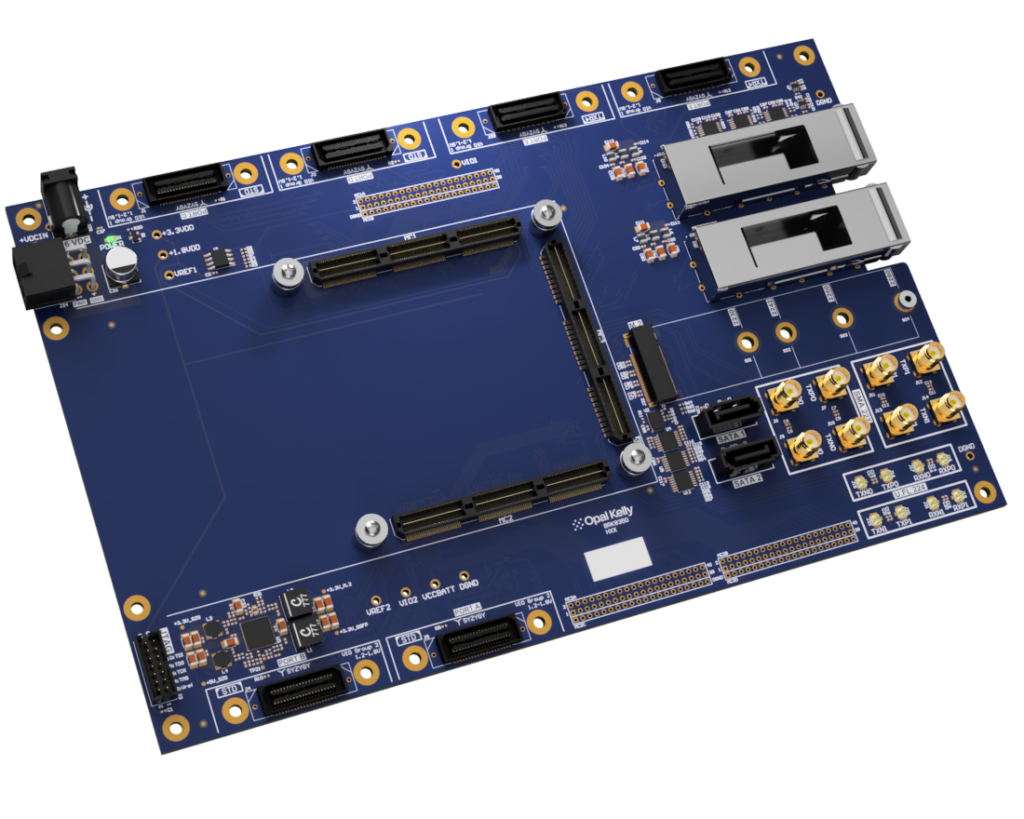

Peripherals and Connectors

The table below summarizes the various connectors on the BRK8350 rev HXX. The XEM8350 Pin List has full connection information in the “BRK8350” columns. Additionally, please refer to the schematics and layout available on the Pins downloads page for detailed connection diagrams.

| CONNECTOR TYPE | REFDES | FPGA BANK |

|---|---|---|

| SYZYGY Standard | J1 | I/O 48 |

| SYZYGY Standard | J2 | I/O 47 |

| SYZYGY Standard | J4 | I/O 45 |

| SYZYGY Standard | J5 | I/O 24 |

| SYZYGY Transceiver (TXR-4) | J8 | GTH 225, I/O 46 |

| SYZYGY Transceiver (TXR-4) | J23 | GTH 128, I/O 46 |

| U.FL | J15-16, J19-20 | GTH 224 |

| SMA | J6-7, J9-14 | GTH 227 |

| SATA | J26-27 | GTH 227 |

| QSFP1 | J30 | GTH 126, I/O 24 |

| QSFP2 | J31 | GTH 127, I/O 25 |

| M.2 | J32 | GTH 226, I/O 45 |

JTAG

The JTAG connections from MC1 are wired to a dedicated 2mm header (J3) compatible with the Xilinx JTAG cable. The JTAG interface presented is at a 1.8V signaling voltage.

| CONNECTOR PIN | JTAG SIGNAL | CONNECTOR PIN | JTAG SIGNAL |

|---|---|---|---|

| 1 | GND | 2 | +1.8V (Vref) |

| 3 | GND | 4 | JTAG_TMS |

| 5 | GND | 6 | JTAG_TCK |

| 7 | GND | 8 | JTAG_TDO |

| 9 | GND | 10 | JTAG_TDI |

| 11 | GND | 12 | NC |

| 13 | GND | 14 | NC |

Clock Oscillator

| CLOCK | FREQUENCY | MC Pins | FPGA PINS (P / N) |

|---|---|---|---|

| MGT REFCLK0 | 100 MHz | MC3 85 / 87 | AH10 / AH9 (Bank 226) |

A PCIE clock generator chip provides a synchronous 100Mhz Gen3 compatible clock to both the M.2 connector and the MGT REFCLK1.

On Rev FXX and previous, this clock was provided to the transceiver ref clock by two separate on-board 100-MHz oscillators.

QSFP+ Transceiver Sockets

The BRK8350 has two QSFP+ cages installed, but the optical transceivers are optional. The following 10Gtek part is one example option.

QSFP control signal I/O connections are listed on the XEM8350 Pin List.

| MANUFACTURER | PART NUMBER | Description | APPROXIMATE COST |

|---|---|---|---|

| 10Gtek | AMQ10-SR4-M1 | 40GBASE-SR4 QSFP+ Transceiver for MMF, 100M | $39.00 / each |

M.2 Socket

The M.2 connector (J32) is an M-keyed Socket 3 interface which supports SATA and PCIe-based SSD applications. The connector fits 22-mm wide modules. A standoff is included for secure mounting of module type 2280, with additional mounting hole options for types 2230, 2242 and 2260.

A PCIE clock generator chip provides a synchronous 100Mhz Gen3 compatible clock to both the M.2 connector (pins 53/55) and the MGT REFCLK1 (Bank 226 AH10 / AH9).

On Rev FXX and previous, this clock was provided to the M.2 connector by two separate on-board 100-MHz MEMS oscillators.

Schematic and Design Files

The BRK8350 schematics and design files are available in the Downloads section of the Pins website.

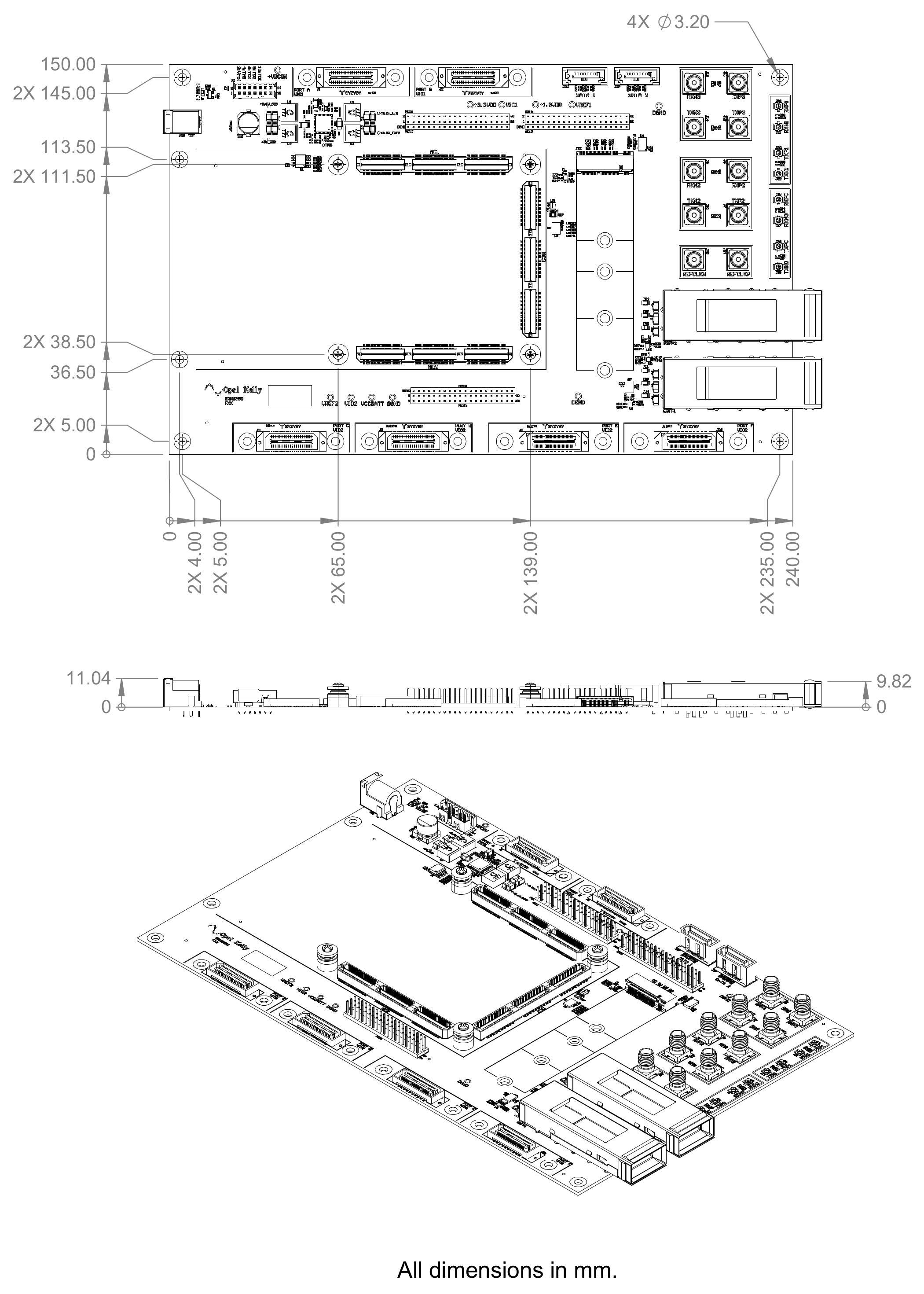

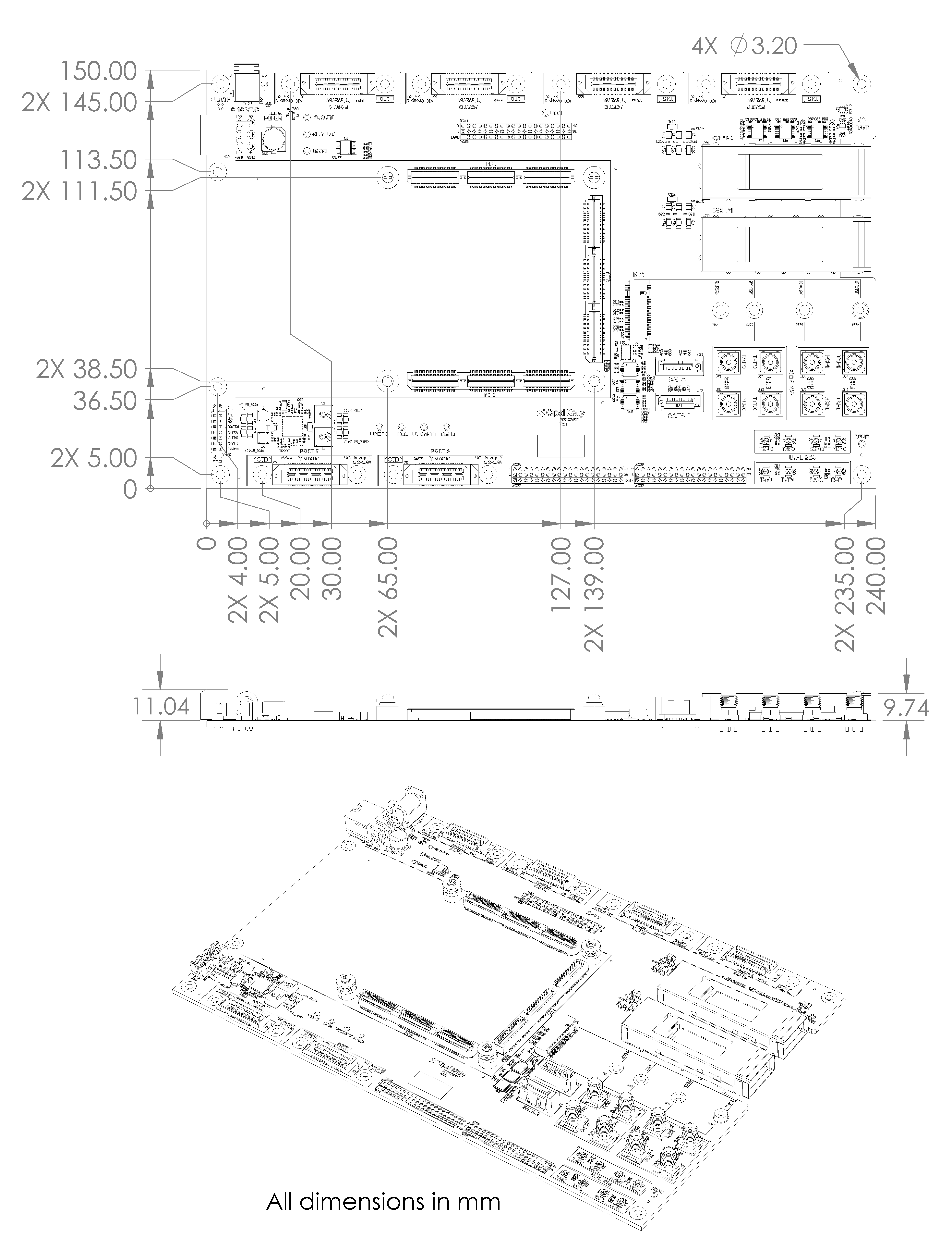

Mechanical Drawing

3D Models are also available in SolidWorks, STEP, and IGES formats.

Rev HXX

Rev FXX