Introduction

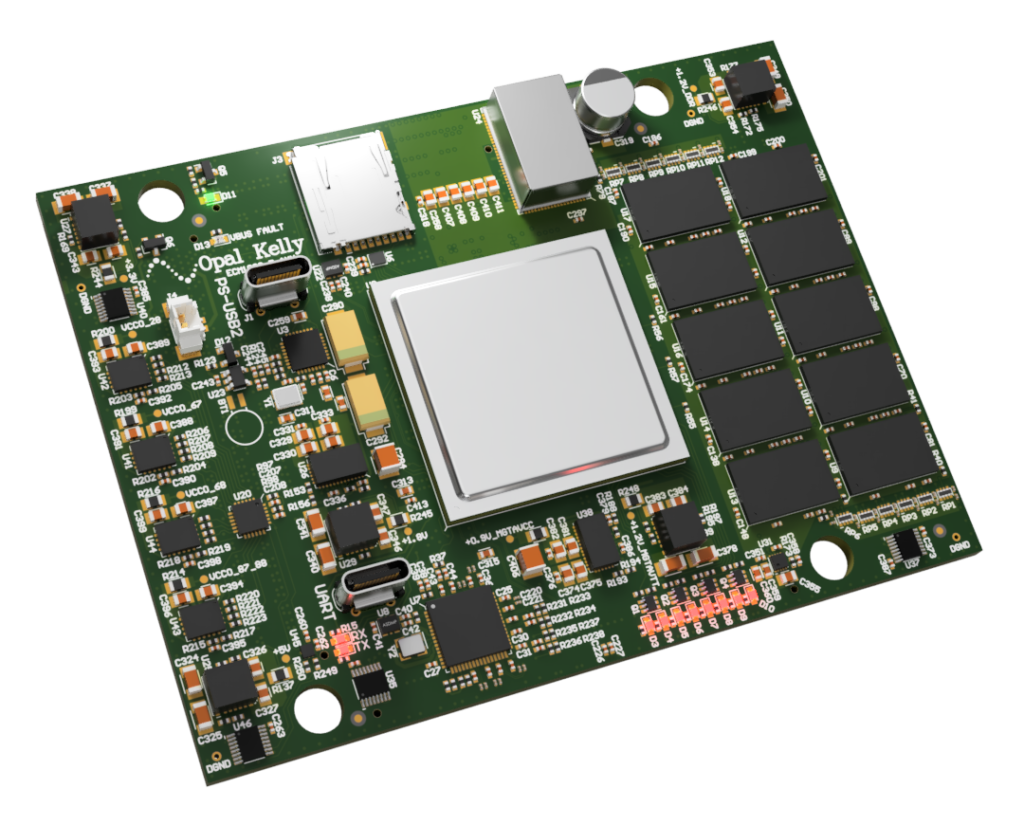

The ECM1900 is a compact FPGA module optimized for edge computing applications. It features a Xilinx Zynq UltraScale+ SoC, two independent 4-GiB DDR4 interfaces, high-efficiency switching power supplies, and three high-density 0.5mm expansions connectors which include full gigabit transceiver capability. A multi-channel, programmable clock generator is attached to the SoC.

Documentation and Reference Materials

The following is a comprehensive list of documentation available for this device.

| ECM1900 User’s Manual | This online documentation space. |

| ECM1900 Pins Reference | The interactive Pins reference for the device provides detailed pinout information as well as automated constraint file generation. Export functionality is provided to PDF, CSV. Constraint files are provided for UCF, XCD (Xilinx) and QSF, SDF (Altera). |

| FrontPanel SDK User’s Manual | The online documentation space for the FrontPanel SDK. |

| FrontPanel API Reference | Online API reference with detailed usage for every API method. |

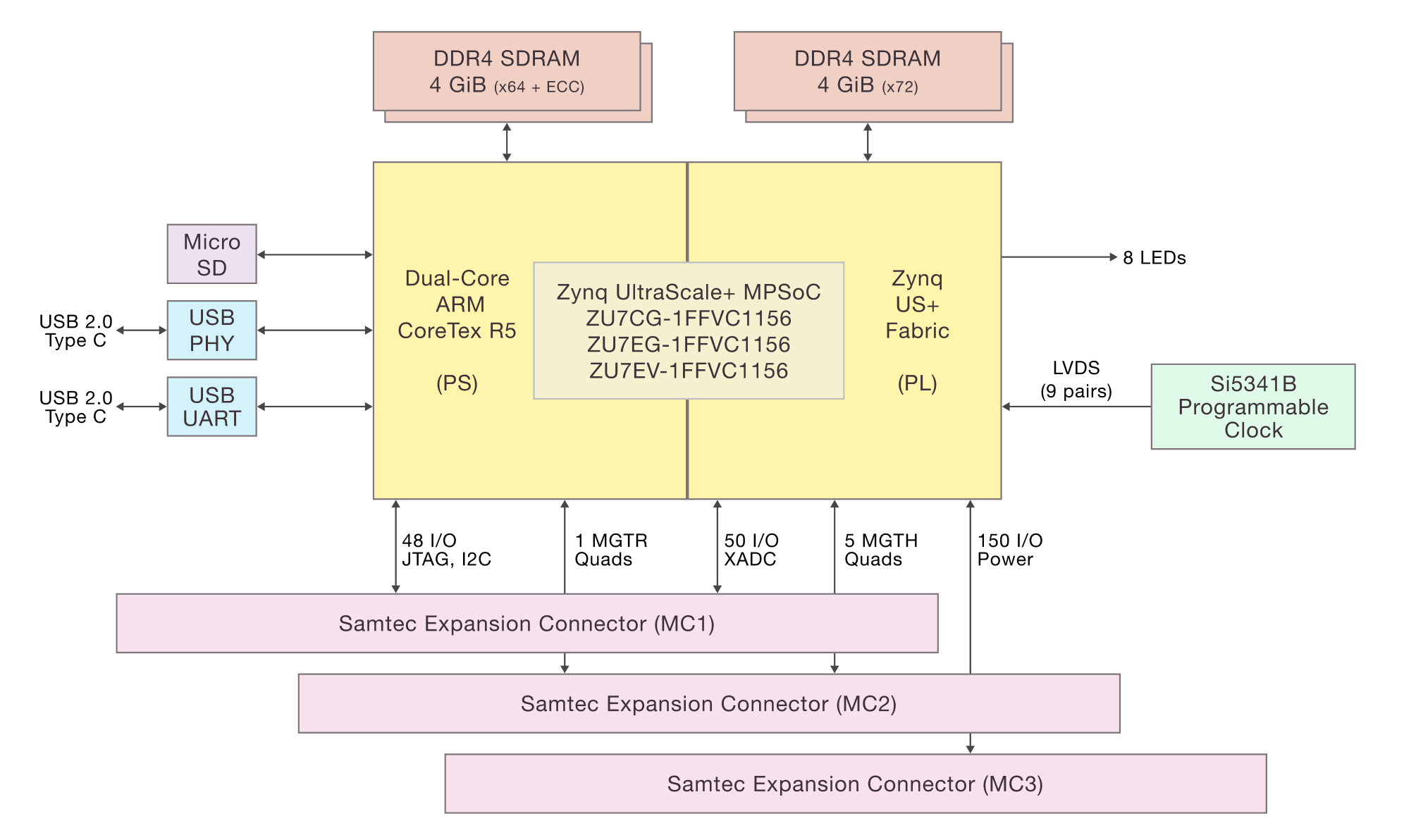

Functional Block Diagram

FPGA

The ECM1900 is offered in three variants. The table below lists some of the features of the device. Please consult the Xilinx documentation for a more thorough overview.

| FEATURE | ECM1900-ZU7CG | ECM1900-ZU7EG | ECM1900-ZU7EV |

|---|---|---|---|

| FPGA | XCZU7CG-1 | XCZU7EG-1 | XCZU7EV-1 |

| System Logic Cells | 504,000 | 504,000 | 504,000 |

| CLB Flip-Flops | 460,800 | 460,800 | 460,800 |

| Distributed RAM | 6.2 Mb | 6.2 Mb | 6.2 Mb |

| Block RAM | 11.0 Mb | 11.0 Mb | 11.0 Mb |

| DSP Slices | 1,728 | 1,728 | 1,728 |

| Clock Management Tiles | 8 | 8 | 8 |

| APU | Dual-core Arm Cortex-A53 | Dual-core Arm Cortex-A53 | Dual-core Arm Cortex-A53 |

| RPU | Dual-core Arm Cortex-R5F | Dual-core Arm Cortex-R5F | Dual-core Arm Cortex-R5F |

| GPU | – | Mali-400MP2 | Mali-400MP2 |

| VCU | – | – | H.264/H.265 |

Power Supply

The ECM1900 is designed to operate from a single 6 V to 15 V power source supplied through mezzanine connector MC3. This provides power to several high-efficiency switching regulators on-board to provide multiple DC voltages for various components on the module.

On-board Peripherals

The ECM1900 is designed to compactly support a large number of applications with a small number of on-board peripherals. These peripherals are listed below.

Clock Generator

A Silicon Labs Si5341B clock generator provides nine user configurable clock signals to the FPGA. Three of these signals are accessible to the FPGA fabric through global clock inputs. The remaining six clock signals are provided as transceiver quad reference clock inputs.

CPU Memory • 4 GiB DDR4

The module includes two separate and independent 4-GiB DDR4 SDRAM interfaces. Attached to the MPSoC DDR controller is a 64-bit interface with support for 8-bit ECC (for a total width of 72 bits). The maximum clock rate of the SDRAM is 1200 MHz for a peak memory bandwidth of 154 Gib/s.

The DDR4 SDRAM part number is Micron MT40A512M16LY-075:E (or compatible).

FPGA Memory • 4 GiB DDR4

The module includes two separate and independent 4-GiB DDR4 SDRAM interfaces. Attached to PL fabric is a 72-bit wide interface which can optionally support ECC. The maximum clock rate of the SDRAM is 1333 MHz. With the -1 speed grade of the Zynq Ultrascale+, the maximum clock rate is 1200 MHz for a peak memory bandwidth of 154 Gib/s.

The DDR4 SDRAM part number is Micron MT40A512M16LY-075:E (or compatible).

MicroSD Memory Slot

A standard MicroSD memory card slot is included and connected to the PS SDIO 1 controller. The PS_MODE boot mode pins are configured to boot to a MicroSD card inserted in this slot by default. The PS SDIO 1 controller supports version SD 3.0. Please see Xilinx’s AR# 66779 for a list of tested SD cards on the Zynq UltraScale+ MPSoC.

LEDs

Eight LEDs are available for general use as indicators.

FPGA Fan Controller

A small connector provides power to an optional fan mounted on the FPGA heat sink. This power is under the control of the Linux OS. The 6-15 VDC input voltage to the board is applied to the fan when active.

Copyright

Software, documentation, samples, and related materials are Copyright © 2006-2021 Opal Kelly Incorporated.

Opal Kelly Incorporated

Portland, OR

https://www.opalkelly.com

All rights reserved. Unauthorized duplication, in whole or part, of this document by any means except for brief excerpts in published reviews is prohibited without the express written permission of Opal Kelly Incorporated.

Opal Kelly® and FrontPanel® are registered trademarks of Opal Kelly Incorporated. Linux is a registered trademark of Linus Torvalds. Microsoft and Windows are both registered trademarks of Microsoft Corporation. All other trademarks referenced herein are the property of their respective owners and no trademark rights are claimed.