Specifications

| Host Interface | USB 3.0 Type-C FrontPanel Support |

| FPGA | XCAU25P-2FFVB676E |

| FPGA Memory | 1 GiByte DDR4 (16-bit wide data interface) |

| NV Memory (System) | 16 MiB SPI Flash |

| NV Memory | 32 MiB QSPI FPGA Flash (supports FPGA gateware boot) |

| Clocks | 100 MHz, 100 MHz, and 125 MHz fixed oscillators |

| FPGA I/O | 104 HP I/O (Banks 66, 67) 68 HD I/O (Banks 84, 86, 87) |

| FPGA MGT | 11 GTY transceivers (16.375 Gb/s) |

| Dimensions | 170mm x 97mm (6.69″ x 3.82″) |

| MINIMUM | TYPICAL | MAXIMUM | UNITS | |

|---|---|---|---|---|

| DC Input | +8.0 | – | +14.0 | VDC |

| DC Input Ripple | – | – | 50 | mVp-p |

| Operating Temperature | 0 | – | +70 | ºC |

| Storage Temperature | -50 | 0 | +100 | ºC |

| Weight | 92 | grams | ||

| Oscillator Frequency (FPGA Fabric) | 100 | MHz | ||

| Oscillator Frequency (DDR4) | 100 | MHz | ||

| Oscillator Frequency (Transceivers) | 125 | MHz |

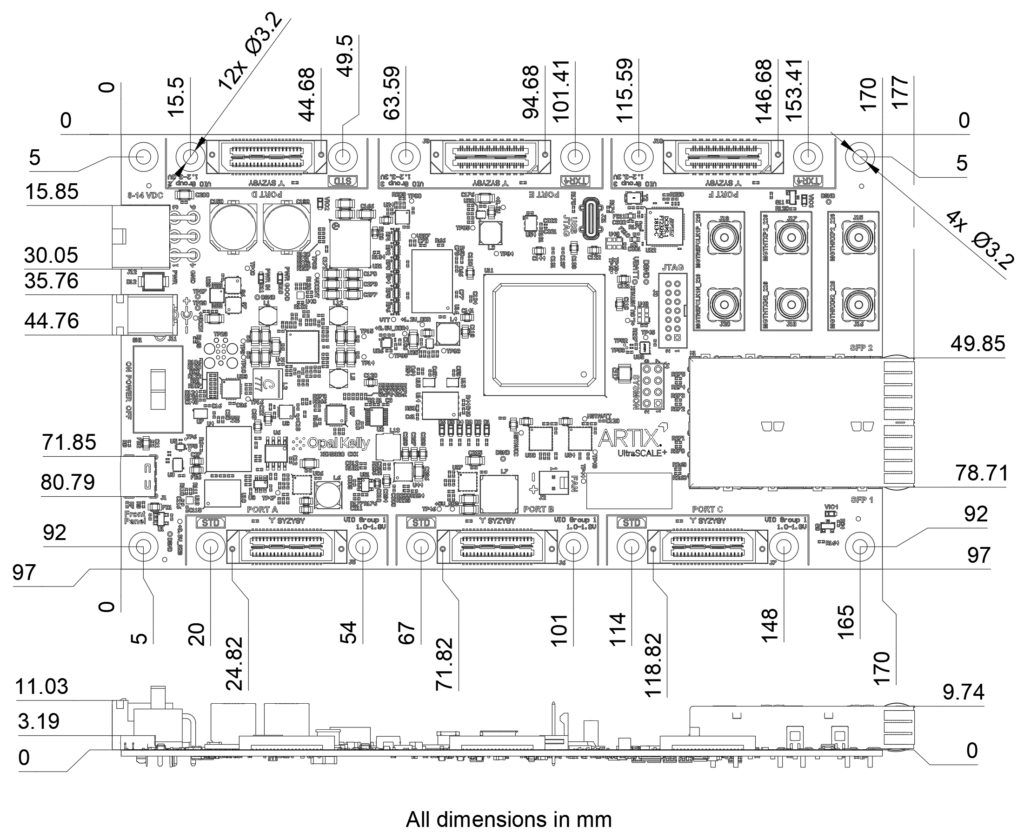

PCB Footprint

The XEM8320 PCB is 170mm x 97mm (6.69″ x 3.82″) with four mounting holes placed at the corners. These mounting holes are electrically isolated from all signals on the XEM8320. Six high-density SYZYGY connectors are located along the two long edges of the PCB. Power, USB Type C, and SFP cages are located long the two short edges of the PCB. Six SMA connectors are a JTAG connector are available and configured for vertical launch connections.

Schematics

Electrical schematics are provided in redacted form through Pins Downloads. The FrontPanel SDK and related design details are proprietary and confidential. Schematic pages related to their implementation have been removed and are unavailable.

Visit Pins Downloads > Design Schematics and Artwork > XEM8320-AU25P-REV-Schematic.pdf

Mechanical Drawing

The mechanical drawing below may be used for enclosure or mounting hardware design. 3D Models are also available in SolidWorks, STEP, and IGES formats. Please note that the XEM8320 is a development platform and not intended for production deployment and is subject to change without notice. For a lifecycle-managed module, please see the companion XEM8310-AU25P module.

SYZYGY Expansion

The XEM8320 supports both SYZYGY Standard and SYZYGY Transceiver (TXR4) peripherals for expansion. For more information, visit syzygyfpga.io and the SYZYGY Ports page.

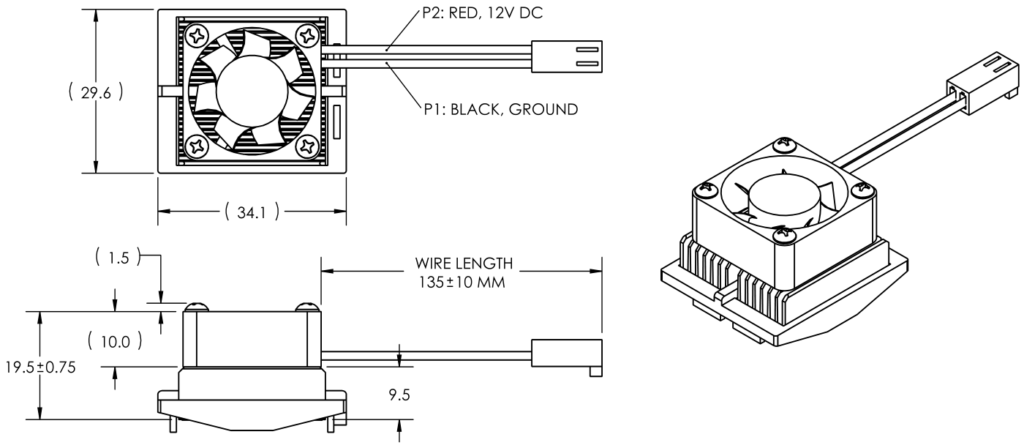

Heat Sink

An active (fan-based) heatsink is installed on the FPGA for cooling. The fan enable can be controlled over the FrontPanel API. See the Device Settings documentation for more information.

The fansink is Radian part number FI27/1.3+Y+T725.