Powering the XEM8320

The XEM8320 requires a clean, filtered, DC supply within the range of 8 V to 14 V. This supply may be delivered through the barrel jack power connector (rated to 5 A max current) or through the 6-pin power connector (rated to 24 A max current).

The included fansink has a nominal operating voltage of 12 V and a recommended operating range of 10.8 V to 13.2 V. The fansink is powered directly by the external power supply connected to the XEM8320. It is recommended to keep the external supply voltage within this range whenever the fansink is enabled.

Power Supply

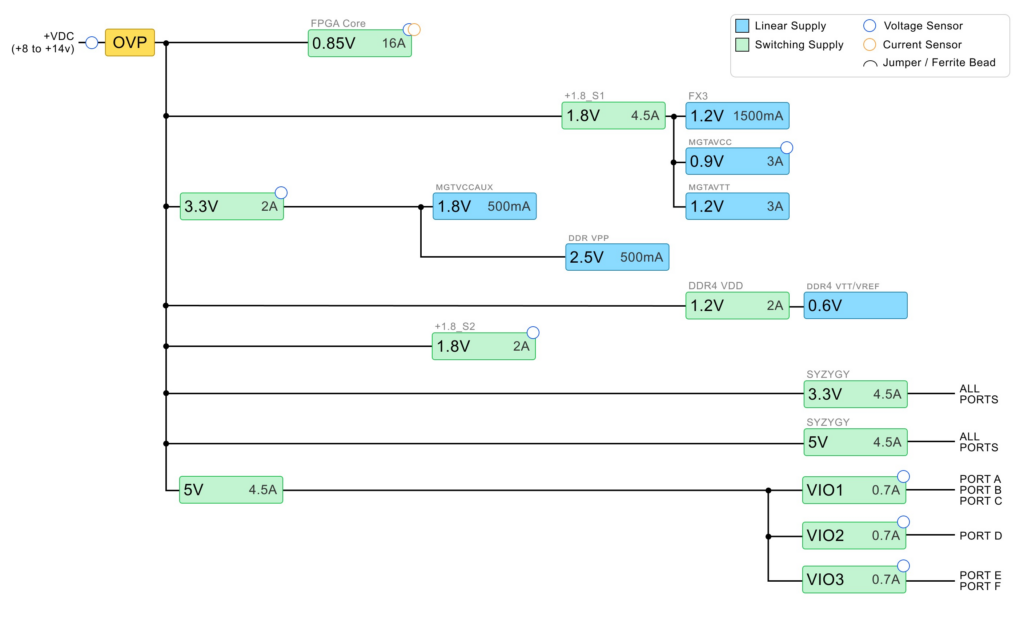

The XEM8320 is designed to be operated from a single power supply of 8 V to 14 V (12 V nominal) supplied through either of the two DC power connectors on the device. This provides power for the several high-efficiency switching regulators on-board to provide multiple DC voltages for various components on the device as well as three software adjustable supplies for the SYZYGY peripherals.

A block diagram of the power distribution system is shown below.

The fansink included with the XEM8320 has an operating range of 10.8 V to 13.2 V, with a nominal operating voltage of 12 V. It is recommended to keep the external supply voltage within this range whenever the fansink is enabled.

Barrel Jack Power Connector

The barrel jack power connector on the XEM8320 is part number PJ-102AH from CUI, Inc. It is a standard “canon-style” 2.1mm / 5.5mm jack. The outer ring is connected to DGND. The center pin is connected to +VDCIN_JACK.

The PJ-102AH jack is rated for 5 A maximum continuous current. Applications requiring higher current are advised to use the 6-pin connector for providing power to the system (rated for a maximum of 24 A).

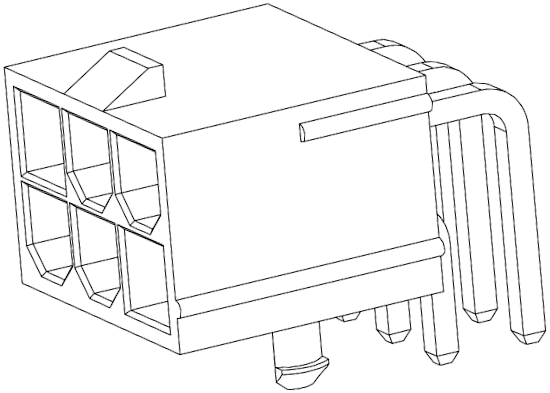

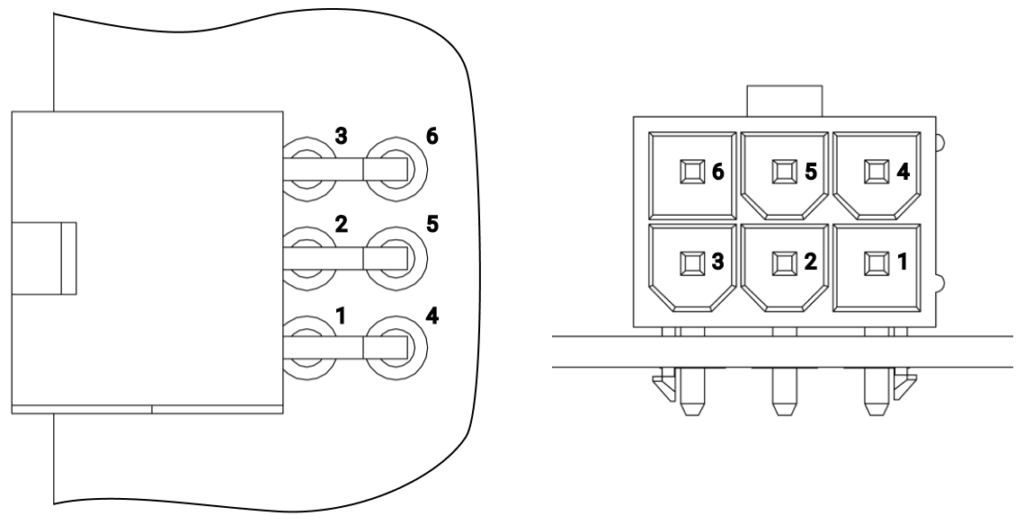

6-Pin Power Connector

The 6-pin connector is a PCIe-style power connector from Molex, part number 0455580003. Pins 1-3 are connected to +VDCIN_JACK, and pins 4-6 are connected to ground. Maximum current is 24 A (8 A per pin).

Over-Voltage Protection and Under-Voltage Lockout

The XEM8320 includes an over-voltage protection circuit which disconnects the input supply from the on-board circuitry when the input is higher than approximately 15.0 V. It is also prevented from powering on when the input supply is below approximately 7.25V. This is determined by the startup voltage of the VCCINT regulator (U21, Murata MYMGM1R816ELA5RA). And it is protected from reverse polarity voltage connected to the input.

LED Indicators

The XEM8320 includes five LED indicators for power status.

| LED | On Condition |

|---|---|

| PWR IN (D11) | +VDCIN present (>4V), no over-voltage or reverse voltage faults |

| PWR GOOD (D10) | All on-board power supplies active and within expected range (Does not include +3.3V_SZG, +5V_SZG, and VIOx supplies) |

| VIO1 (D13) | VIO1 power supply enabled |

| VIO2 (D14) | VIO2 power supply enabled |

| VIO3 (D15) | VIO3 power supply enabled |

SYZYGY Power Sequencing

Power to the +5V and +3.3V SYZYGY rails are enabled shortly after power-on. Voltage and timing of powering the VIO rails on the three SYZYGY power groups depends on the XEM8320_SMARTVIO_MODE device setting. See the SYZYGY Ports documentation for more information.

Power Budget

The table below can help you determine your power budget for each supply rail on the XEM8320. All values are highly dependent on the application, speed, usage, and so on. Entries we have made are based on typical values presented in component datasheets or approximations based on AMD power estimator results. Shaded boxes represent unconnected rails to a particular component. Empty boxes represent data that the user must provide based on power estimates.

The user may also need to adjust parameters we have already estimated (such as FPGA VCCO values) where appropriate. All values are shown in milliwatts (mW) unless otherwise specified.

| COMPONENT(S) | 0.85 V | 1.2 V | 1.8 V S1 | 1.8 V S2 | 3.3 V |

|---|---|---|---|---|---|

| FPGA VCCINT, VCCINT_IO, VCCBRAM | |||||

| FPGA VCCAUX, VCCAUX_IO, VCCADC | 974 | ||||

| Clock oscillators | 287 | ||||

| FPGA MGTYAVCC | 2,090 | ||||

| FPGA MGTYAVTT | 4212 | ||||

| FPGA MGTYVCCAUX | 297 | ||||

| FX3 USB host interface | 468 | 180 | |||

| DDR4 VDD/VDDQ | 316 | ||||

| DDR4 VTT termination | 461 | ||||

| DDR4 VPP | 66 | ||||

| SFP | |||||

| FPGA VCCO | 180 | 16 | |||

| Total (mW) | 956 | 6,770 | 1,170 | ||

| Available (mW) | 13,600 | 2,400 | 8,100 | 3,600 | 6,600 |

| COMPONENT(S) | 3.3 V SZG | 5.0 V SZG | VIO1 | VIO2 | VIO3 |

|---|---|---|---|---|---|

| FPGA VCCO | |||||

| SYZYGY Group 1 | |||||

| SYZYGY Group 2 | |||||

| SYZYGY Group 3 | |||||

| Total (mW) | |||||

| Available (mW) | 14,850 | 22,500 | 1000 mA 1.0-1.8 V | 1000 mA 1.2-3.3 V | 1000 mA 1.2-3.3 V |

Example FPGA Power Consumption

AMD Power Estimator (XPE) version 2020.2.2_1 was used to compute the following power estimates for the VCCINT supply. These are simply estimates; your design requirements may vary considerably. The numbers below indicate approximately 80% utilization.

| COMPONENT | PARAMETERS | VCCINT POWER (MW) |

|---|---|---|

| Clock | 200 MHz GCLK, 200,000 fanout | 986 |

| Clock | 300 MHz GCLK, 75,000 fanout | 628 |

| Clock | 100 MHz GCLK, 100,000 fanout | 272 |

| Clock | 667 MHz GCLK, 50,000 fanout | 963 |

| Logic | 200 MHz, 58,000 logic LUTs, 20,000 shift registers, 20,000 distributed RAMs, 150,000 registers | 1,566 |

| Logic | 300 MHz, 8,000 logic LUTs, 75,000 registers | 583 |

| Logic | 667 MHz (DDR4), 16,000 logic LUTs, 50,000 registers | 1,149 |

| BRAM | 18-bit, 200 MHz, 280 block RAMs, 50% toggle rate | 519 |

| BRAM | 36-bit, 300 MHz, 140 block RAMs, 50% toggle rate | 920 |

| DSP | 300 MHz, 1090 slices, 12.5% toggle rate | 1,503 |

| GTY | 11 channels, 16.3 Gb/s | 727 |

| Misc. | DCM, PLL, VCCINT_IO, etc. | 100 |

| Total | 9,916 mW | |

| Available | 13,600 mW |