Configuration Banks

Bank 0 and Bank 65 Connections

The FrontPanel SDK and related design details are proprietary and confidential. Schematic pages related to their implementation have been removed and are unavailable. This includes some of the details of the Bank 0 and Bank 65 configuration connections that FrontPanel uses to add advanced configuration features that are beyond the scope of a reference design.

For full details on the available configuration options see UG570 UltraScale Architecture Configuration User Guide from AMD. For a schematic based UltraScale+ configuration implementation see the AMD KCU116 Evaluation design.

FPGA Flash

See the Flash Memory page for details on the FPGA flash connection.

VCCO

Bank 0 and Bank 65 VCCO are powered by 1.8V.

Configuration Mode

FrontPanel provides fast configuration over USB while also enabling gateware to be stored in onboard flash. The full design of this advanced configuration control is proprietary, but the FPGA Flash section of the Flash Memory page shows the XEM8320’s implementation of the “Master SPI Quad (x4)” configuration mode listed in UG570.

JTAG Connections

JTAG and SYSMON connections on Bank 0 are connected to on-board headers with minimal additional components. For details see the JTAG and SYSMON page.

FPGA Temperature Diode

The FPGA internal temperature diode is connected to onboard hardware to monitor its value. This information is provided via FrontPanel and the Device Sensors API. See Device Sensors for more information.

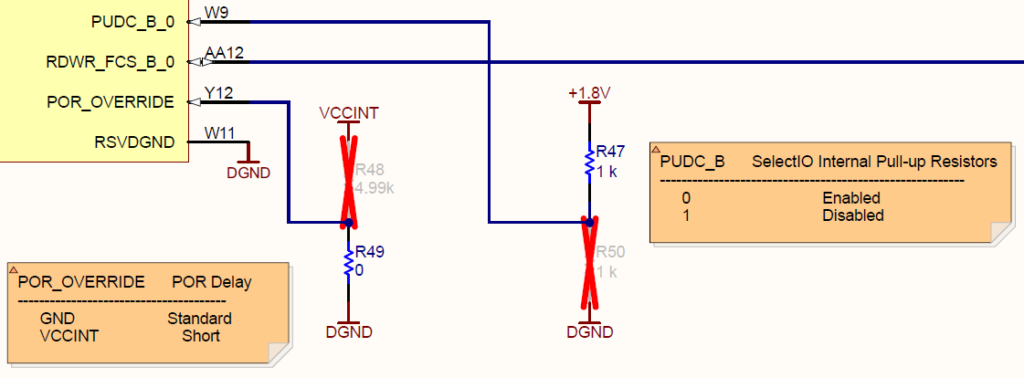

SelectIO Resistors and POR Delay

SelectIO pull resistors and POR delay are configured for correct operation of the XEM8320 and other system components. Adjusting them is not recommended.

DONE_0, INT_B_0, PROGRAM_B_0

These signals are all controlled or monitored automatically by FrontPanel firmware for the specific

configuration modes required of the system. AMD FPGAs support a wide variety of configuration

options for various system requirements. Please see the UG570 UltraScale Architecture Configuration User Guide from AMD for further details.