Introduction

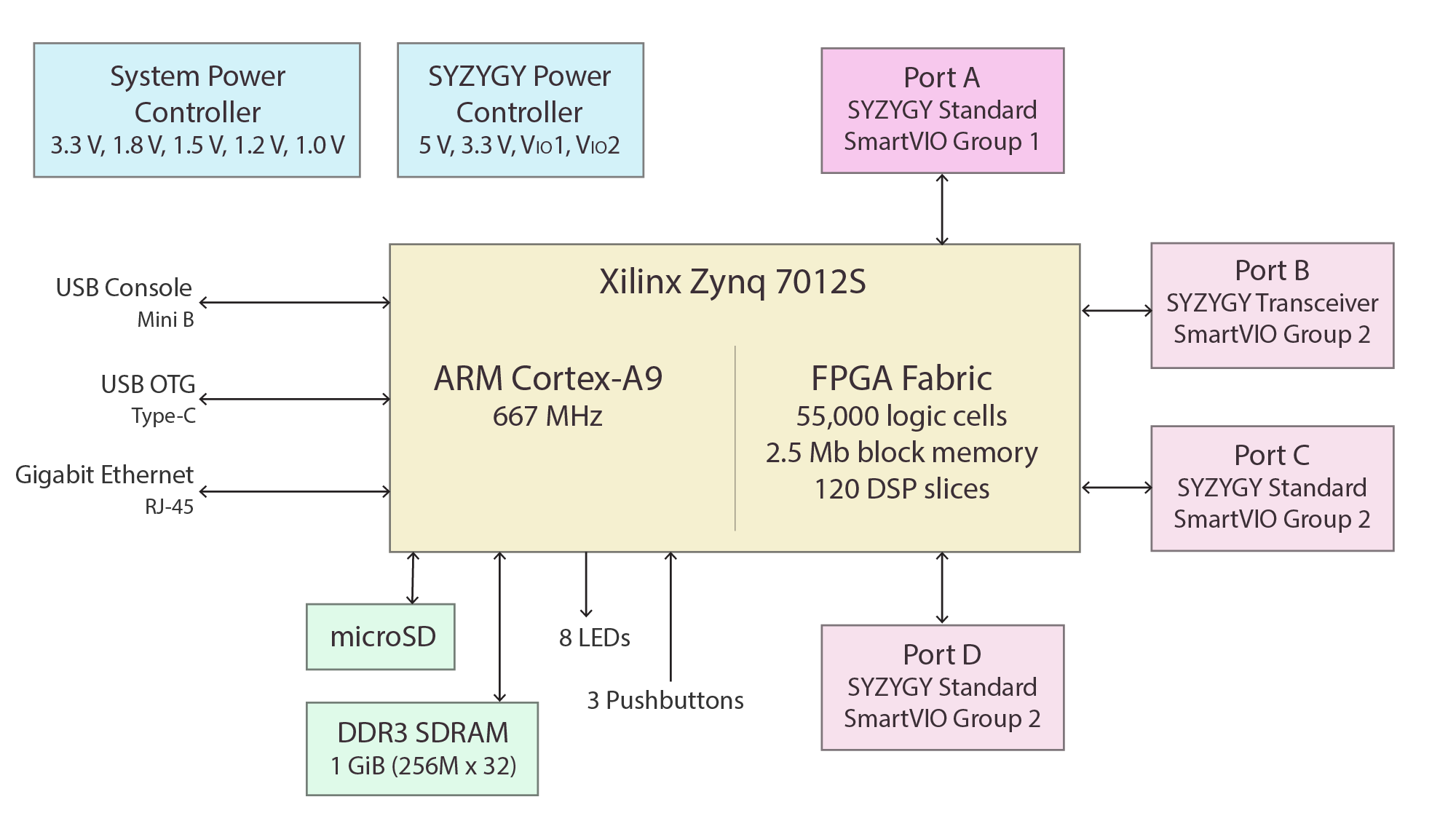

The Brain-1 is an open, modular ARM + FPGA development platform featuring the new SYZYGY standard for high-performance peripherals. Designed as a full-featured development platform, the Brain-1 provides access to over 100 I/O pins on its 484-pin Zynq-7000 device through SYZYGY expansion connectors and has 1-GiByte DDR3 SDRAM available to the SoC.

Functional Block Diagram

FPGA

The table below lists some of the features of the Zynq-7000 SoC on the Brain-1. Please consult the Xilinx documentation for a more thorough overview.

| FEATURE | BRAIN-1 |

|---|---|

| FPGA | XC7Z012S-CLG485-1 |

| CPU | Single-core ARM Cortex-A9 MPCore |

| CPU Extensions | NEON and Single/Double Precision Floating Point |

| CPU Frequency | 667 MHz (-1 speed grade) (*) |

| Logic Cells | 55,000 |

| Flip-Flops | 68,800 |

| LUTs | 34,400 |

| Block RAM | 2.5 Mb |

| DSP Slices | 120 |

| Clock Management Tiles | 3 |

(*) – Note: Due to the use of a 50 MHz reference clock, the CPU Frequency on the Brain-1 is limited to a maximum rate of 650 MHz.

Power Supply

The Brain-1 is designed to be operated from a single 4.5 V to 18 V power source supplied through the DC power jack on the device. This provides power for the several high-efficiency switching regulators on-board to provide multiple DC voltages for various components on the device as well as three adjustable supplies for the peripheral.

DC Power Connector

The DC power connector on the Brain-1 is part number PJ-102AH from CUI, Inc. It is a standard “canon-style” 2.1mm / 5.5mm jack. The outer ring is connected to DGND. The center pin is connected to +VDC.

On-board Peripherals

The Brain-1 is designed to compactly support a large number of applications with a large number of on-board peripherals. These peripherals are listed below.

Low-Jitter Crystal Oscillators

A fixed-frequency, 50 MHz, low-jitter oscillator is included on-board and outputs to the PS section of the SoC. The Zynq SoC can produce a wide range of clock frequencies using the on-chip PLL capabilities.

1-GiByte Quad-Wide DDR3 Synchronous DRAM

The Brain-1 includes a 1-GiByte DDR3 SDRAM with a full 32-bit quad-wide interface to the SoC. This SDRAM is attached to the CPU portion of the SoC, though high rate data transfers can be made from the PL (programmable logic) portion of the SoC through high speed AXI ports. With the -1 speed grade of the Zynq-7000, the maximum clock rate is 533 MHz for a supported peak memory bandwidth of 34 Gib/s.

The DDR3 SDRAM is a Micron MT41K256M16HA-125:E (or compatible).

1-Gbps Ethernet

An Ethernet PHY and RJ-45 connector are connected to the CPU portion of the SoC, allowing transfers up to 1 Gbps to the Brain-1 Zynq SoC.

High Speed USB 2.0 Type-C

A USB 2.0 Type-C port and accompanying PHY add USB host and device capabilities to the Brain-1 SoC. This allows for connection of mass storage devices, network adapters, and more to the Brain-1’s Zynq SoC.

USB to UART Bridge

The Zynq SoC UART is connected through an FTDI USB to UART adapter and a Mini-B USB port on the Brain-1. This connection enables users to view boot messages from the SoC and interact with the Linux command line through a tty interface on a host PC.

LEDs

Eight LEDs are available for general use as indicators.

Expansion Connectors

Peripheral expansion on the Brain-1 is provided through a set of 4 SYZYGY connectors, consisting of three Standard ports and one Tranceiver port.. These expansion connectors provide user access to adjustable IO voltage rails and 118 I/O pins on the FPGA, including several MRCC clock inputs.

Please see the SYZYGY website for more information on the SYZYGY Standard. A number of peripherals are available for purchase on the Brain-1 Crowd Supply page.