Gigabit Transceivers

Access to four high-speed serial transceiver pairs (4 Rx and 4 Tx) corresponding to GTP bank 216 on the FPGA are available on the expansion connectors. MGTREFCLK0 and MGTREFCLK1 of bank 216 are also routed to expansion connectors.

AC-Coupling

AC-coupling capacitors are not installed for any of the GTP transmit or receive pairs or for the MGTREFCLK pairs. If AC-coupling is desired or required for the serial application, they should be installed on the peripheral side (your board).

IBERT Configuration

Xilinx provides the IBERT tool to test and experiment with gigabit transceivers. The settings below are compatible with the XEM7310MT using Vivado 2019.1:

| PROTOCOL DEFINITION | |

|---|---|

| Silicon Version | General ES / Production |

| Protocol | Custom 1 |

| Line Rate | 3.75 Gbps |

| Data Width | 16 |

| Ref Clk | 125.000 MHz |

| Quad Count | 1 |

| PLL Used | PLL0 |

| PROTOCOL SELECTION | |

| GTP Location | QUAD_216 |

| RefClk Selection | MGTREFCLK0_216 |

| TXUSRCLK Source | Channel 0 |

| CLOCK SETTINGS | |

| Add RXOUTCLK Probes | Unchecked |

| Clock Type | System Clock |

| Source | QUAD216_0 |

| I/O Standard | N/A |

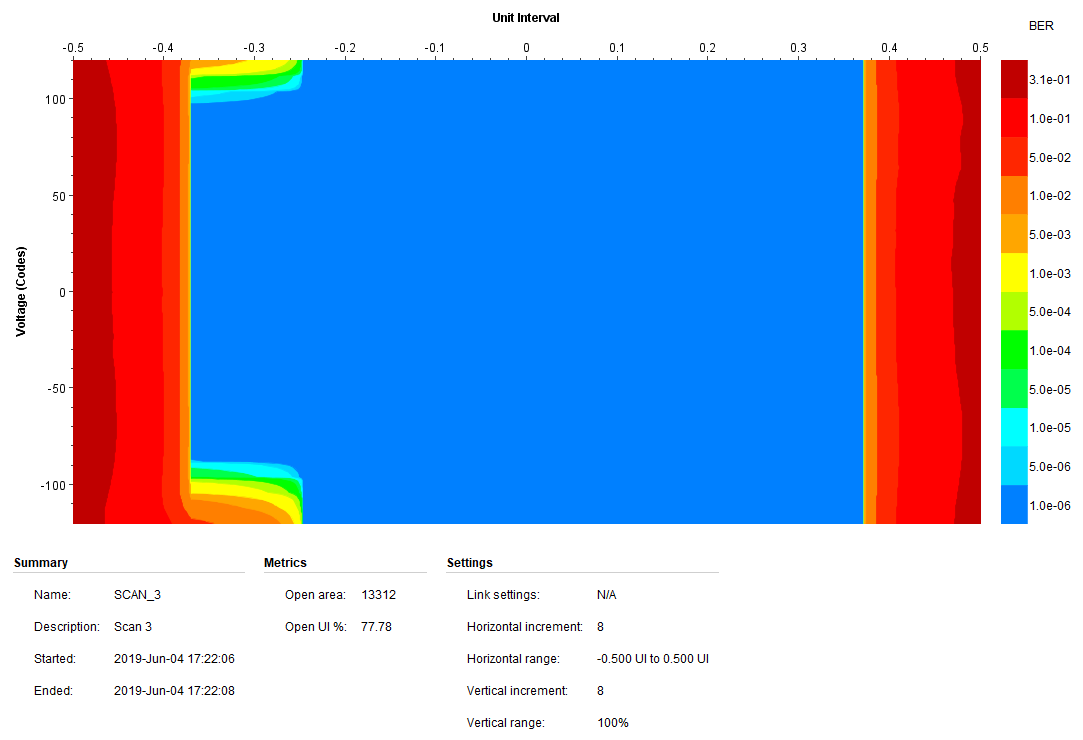

Gigabit Transceiver IBERT Performance

Xilinx’s IBERT tool enables an automated self-measurement of a GTP channel’s eye diagram when used in a loopback mode. Eye diagrams were captured using this tool with a simple loopback peripheral attached to the expansion headers. While results may vary, these are typical captures and actually represent the worst case capture over all channels for the respective rates.

Note that in loopback modes, it can be helpful to disable the DFE (decision feedback equalizer) to avoid over-compensation. In these test cases, the DFE has been left enabled.

3.75 Gbps / XEM7310MT-A75