DDR3 Memory Walkthrough

Generating the Memory Interface Controller

Begin by selecting the “DDR3 SDRAM Controller with UniPHY from the Quartus II IP Catalog. In the newly opened window enter a file name for the IP and select Verilog, press OK.

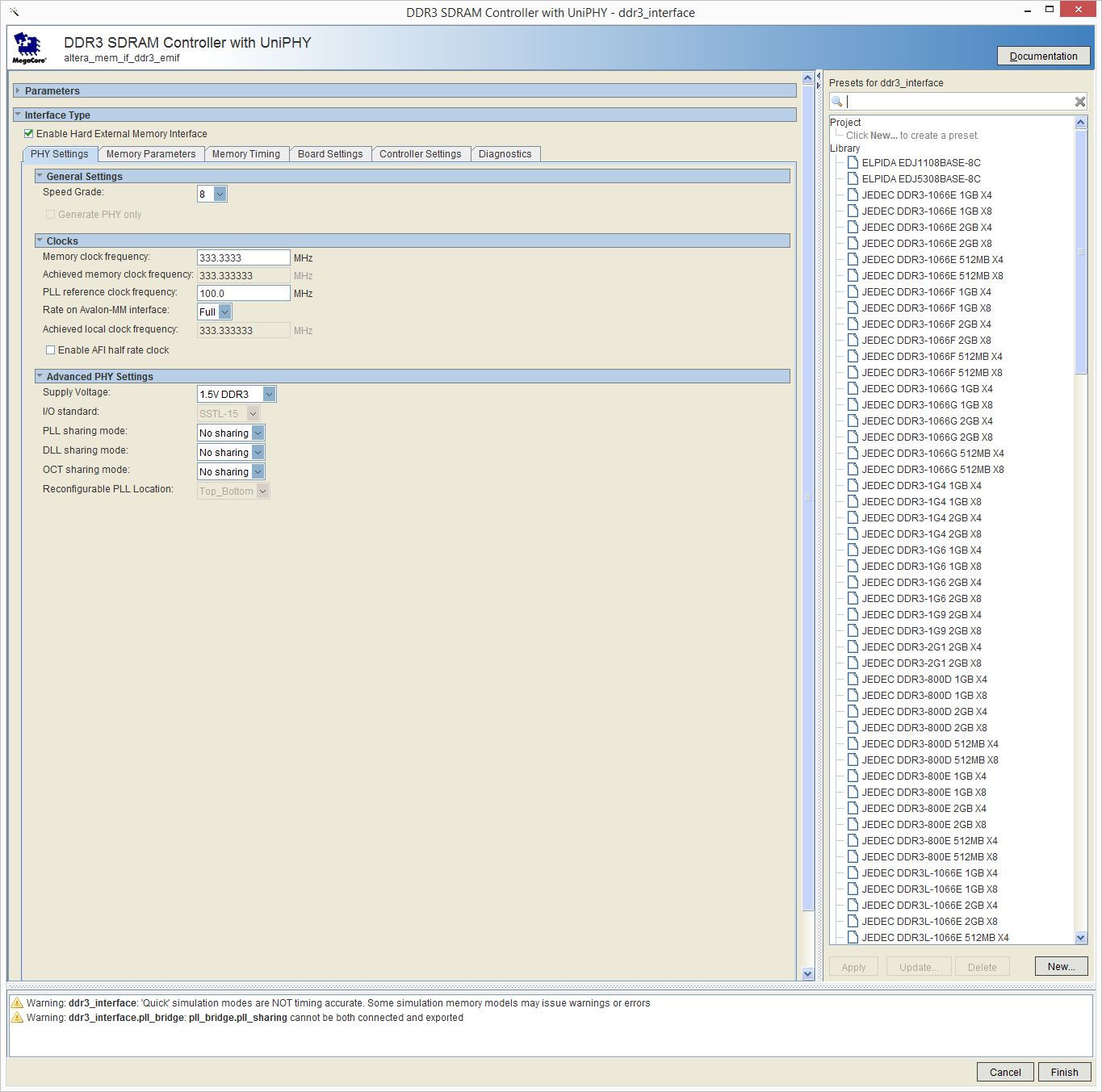

PHY Settings

The Controller Parameters window should appear starting on the PHY Settings tab.

- Check the box at the top to “Enable Hard External Memory Interface” and set the speed grade to 8.

- Enter 333 MHz for the Memory clock frequency and 100 MHz for the PLL reference clock frequency.

- The window should now appear with the settings as shown here:

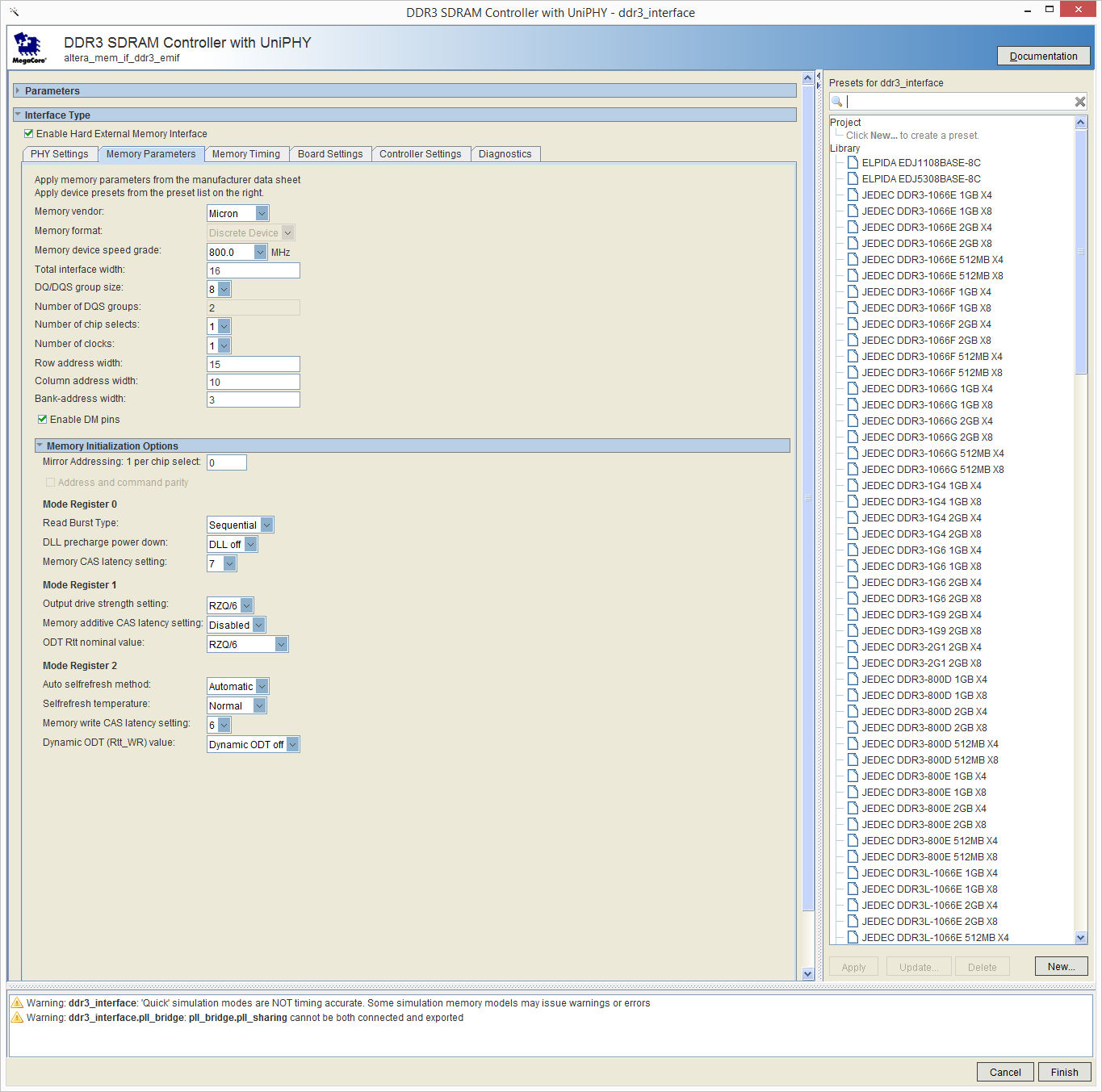

Memory Parameters

In the search box on the right of the window,

- Select the MICRON MT41K256M16HA-125 preset and click “Apply”.

- Select the Memory Parameters tab.

- Change the ODT Rtt nominal value to RZQ/6 in Mode Register 1 and set the Auto selfrefresh method to Automatic in Mode Register 2.

- The Memory Parameters should appear as below:

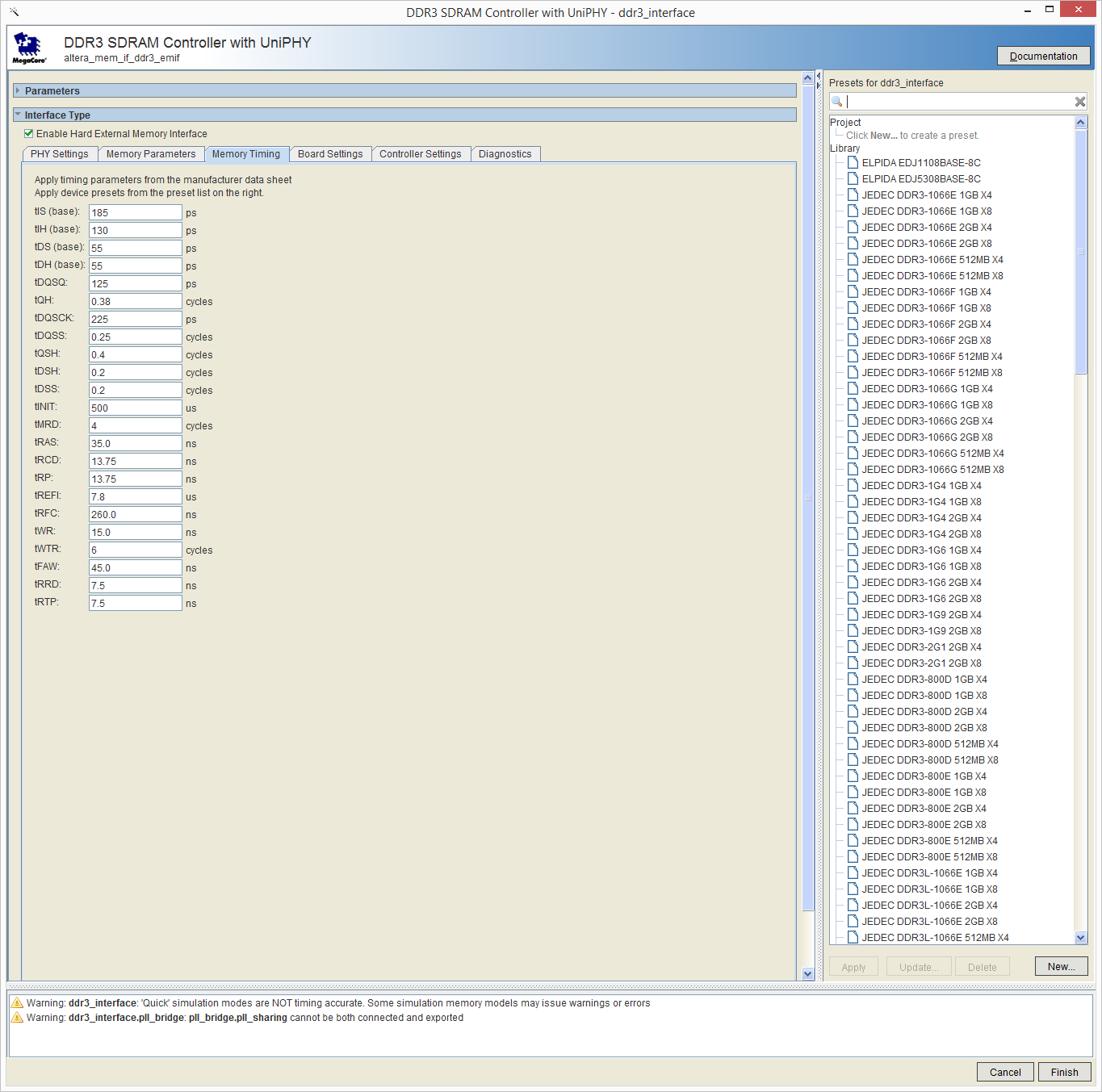

Memory Timing

The default settings for the memory timing are correct and can be seen below:

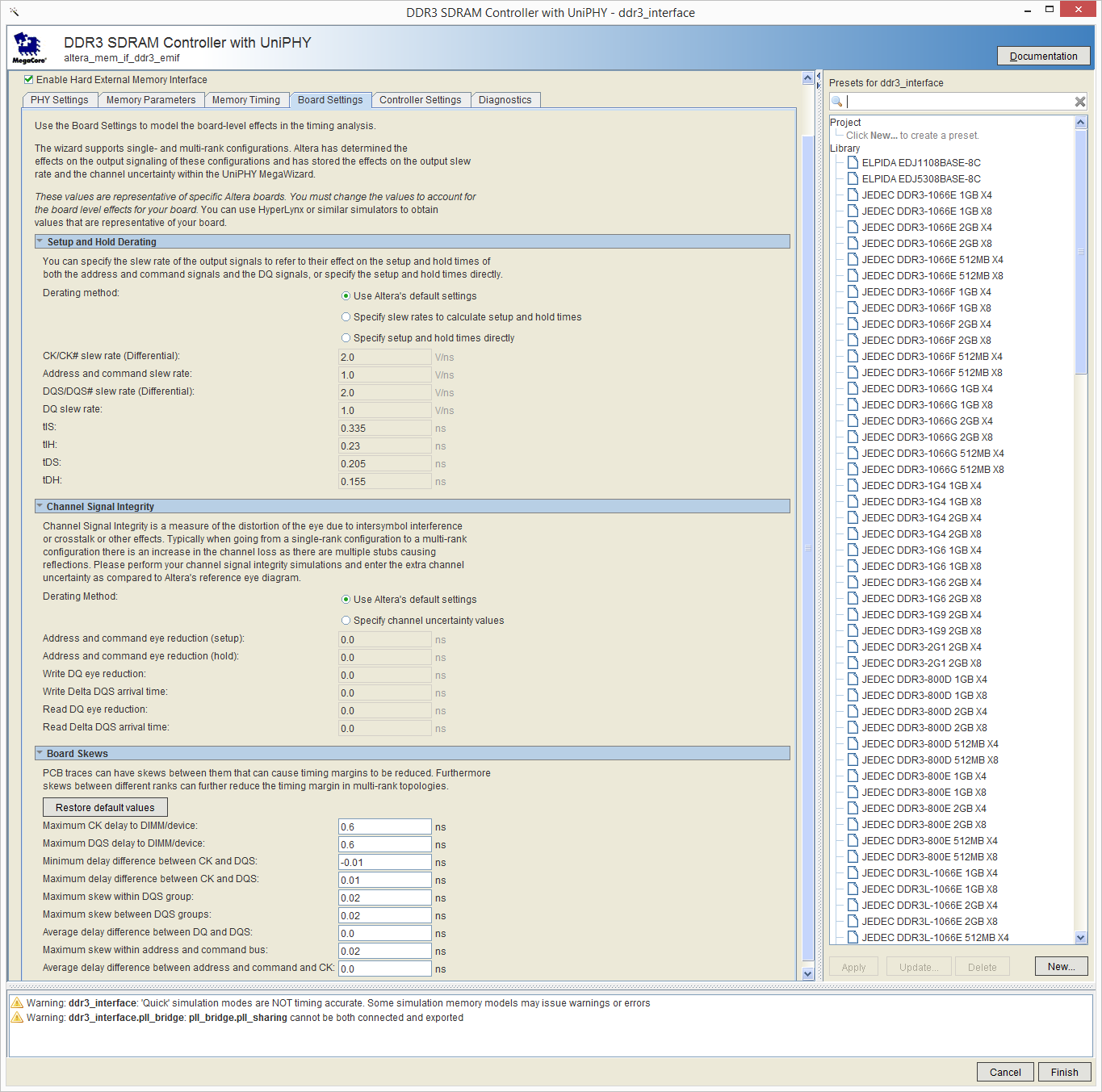

Board Settings

Alteras default board settings work for the interface on the ZEM5305 and can be seen below for reference:

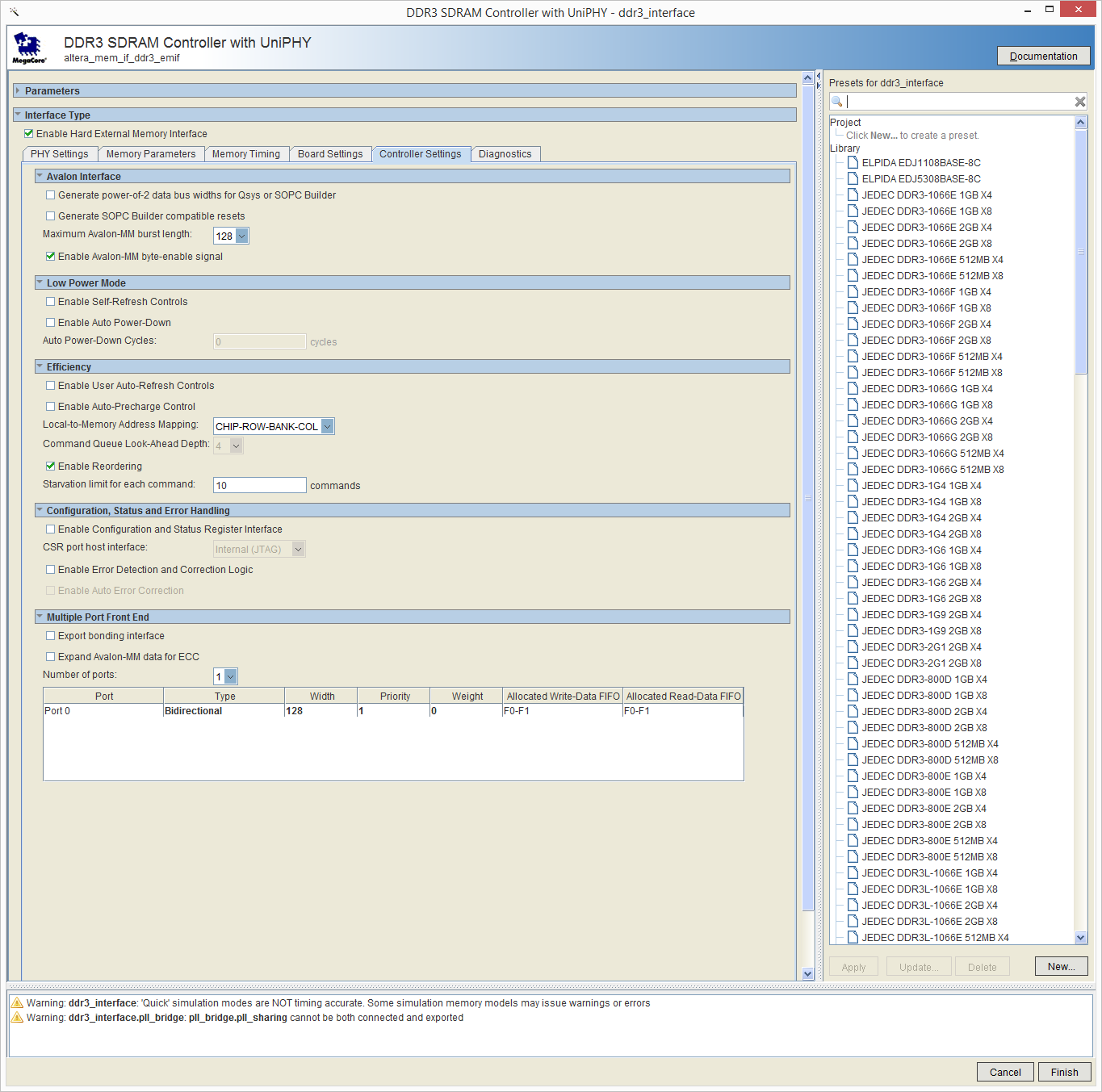

Controller Settings

In the Controller Settings tab set the Maximum Avalon-MM burst length to 128 and set Port 0 of the Multiple Port Front End to a bidirectional port with a 128-bit width, priority 1 and a weight of 0, as seen in the image below:

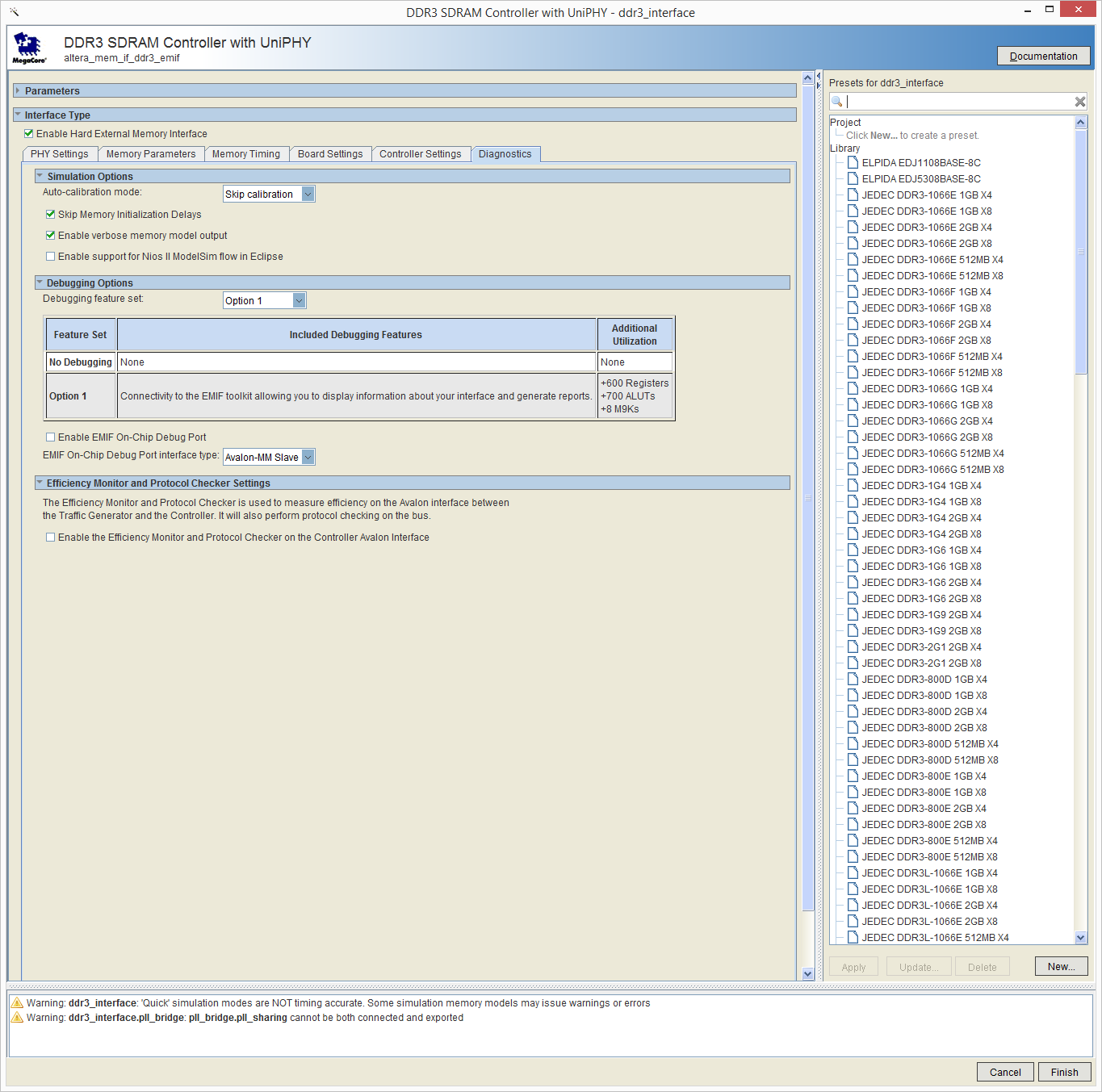

Diagnostics

The default settings in the Diagnostics tab will work for this memory interface. These can be seen below: