BRK5305 Breakout Board

The BRK5305 Breakout Board is a simple reference design intended to mate to the ZEM5305 and provide easy, low-density access to the signals on the high-density mezzanine connectors on the ZEM5305. The BRK5305 also provides necessary power supplies to the ZEM5305 as well as a JTAG header compatible with the Byte Blaster Programmer.

Schematics and Layout

The BRK5305 schematic and layout are available as an Altium Designer project. If you use Altium Designer, you may start with this project as a way to build your own peripheral.

Power Supplies

| SUPPLY | VOLTAGE | MAX CURRENT | PART NUMBER | TYPE |

|---|---|---|---|---|

| +1.1VDD | 1.1 V | 6 A | Altera EN5364QI | Switching |

| +1.2VDD | 1.2 V | 1 A | Texas Instruments TPS7A7100RGWT | Linear |

| +1.5VDD | 1.5 V | 1 A | Texas Instruments TPS7A7100RGWT | Linear |

| +2.5VDD | 2.5 V | 1 A | Texas Instruments TPS7A7100RGWT | Linear |

| +3.3VDD | 3.3 V | 1 A | Texas Instruments TPS7A7100RGWT | Linear |

Switches

SW1 controls the regulation voltage of U3, the linear regulator that establishes the DDR3 voltage. This can be used to set the voltage to 1.35 V (as used by DDR3L parts) or 1.5 V (as used on standard DDR3). The memory device on the ZEM5305 will operate at either voltage.

SW2 controls the PWR_EN (power enable) pin on all of the power supplies on the BRK5305. If you switch this to the off position, all supplies will be disabled.

SW3 selects the +VDC input voltage for all supplies on the BRK5305. In the +5VDC position, the power connector is the input source for all supplies. In the +5VUSB position, the USB power from the ZEM5305 USB connector is used as the input source.

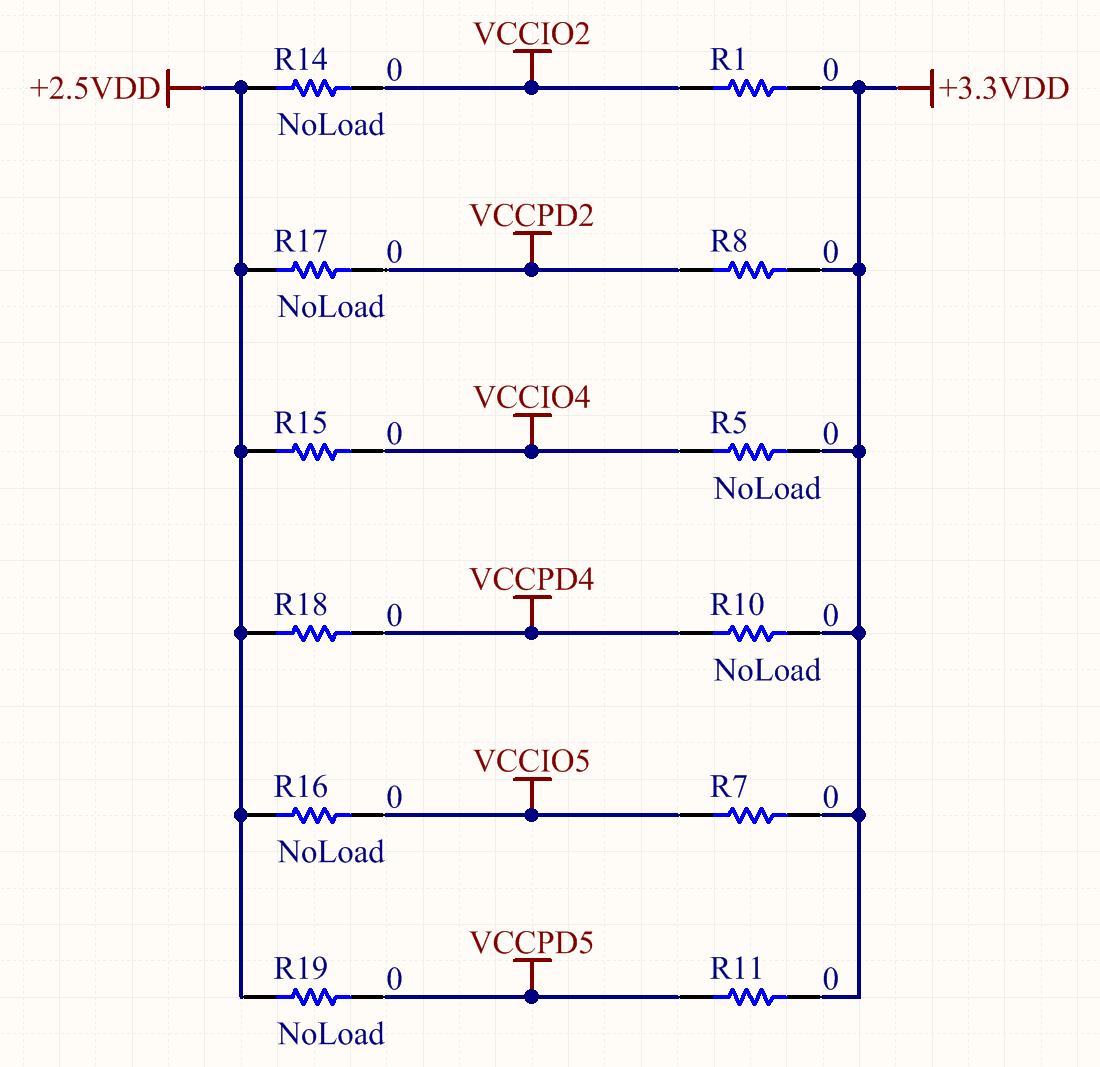

I/O Bank Triples

The three I/O bank triples for banks 2, 4, and 5 are selectable with 12 resistors located on the top layer of the PCB. You can selectively remove and populate these resistors to control the VCCIO and VCCPD supplies for the I/O banks. If you need to set a value other than +2.5 V or +3.3 V for VCCIO, you can remove both resistors and apply the voltage externally.

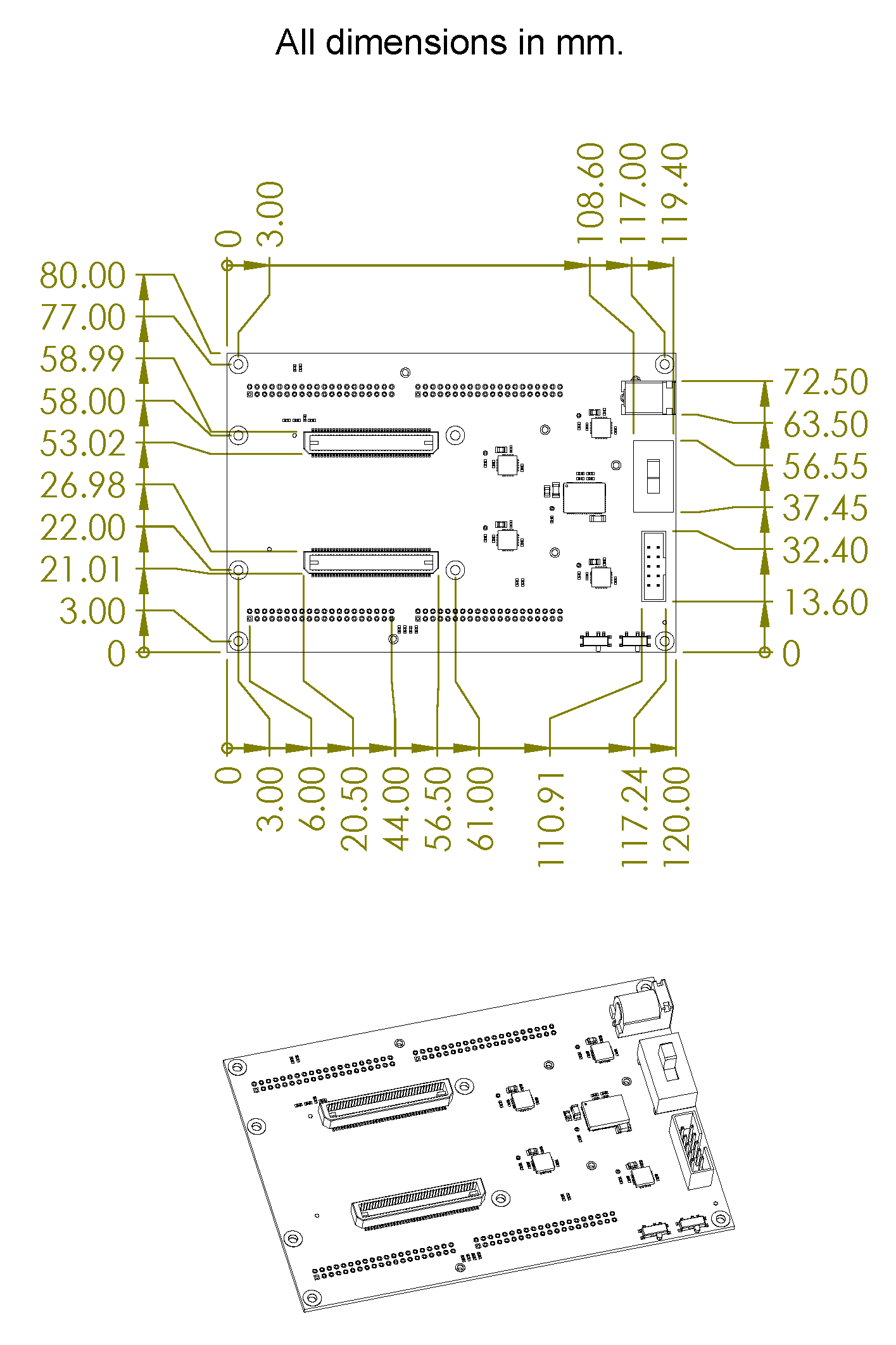

Mechanical Drawing