Powering the XEM7320

The XEM7320 requires a clean, filtered, DC supply within the range of 4.5 V to 18 V. This supply must be delivered through the DC power connector.

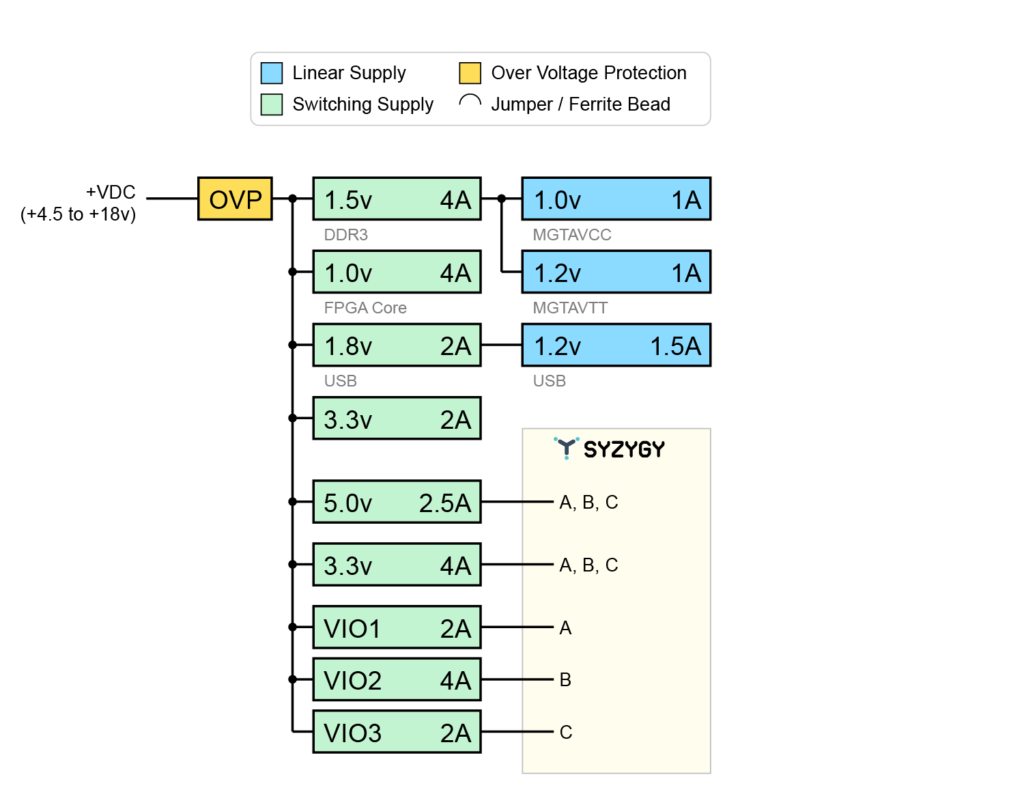

The XEM7320 power distribution system includes several supplies designed to provide suitable, efficient power for several systems and modules. A schematic diagram of the system follows, with input (+VDC) shown to the left and accessible supply rails shown to the right.

Power Supply

The XEM7320 is designed to be operated from a single DC power source supplied through the DC power jack on the device. The input range of this supply must be a clean, well-regulated supply between +4.5VDC to +18VDC. This provides power for the several high-efficiency switching regulators on-board to provide multiple DC voltages for various components on the device as well as three adjustable supplies for the peripheral.

DC Power Connector

The DC power connector on the XEM7320 is part number PJ-102AH from CUI, Inc. It is a standard “canon-style” 2.1mm / 5.5mm jack. The outer ring is connected to DGND. The center pin is connected to +VDC.

Powering via USB

The XEM7320 is not designed or intended to be operated from USB power. USB 3.0 power specifications cannot meet the inrush demands of the XEM7320.

Power Budget

The table below can help you determine your power budget for each supply rail on the XEM7320. All values are highly dependent on the application, speed, usage, and so on. Entries we have made are based on typical values presented in component datasheets or approximations based on Xilinx power estimator results. Shaded boxes represent unconnected rails to a particular component. Empty boxes represent data that the user must provide based on power estimates.

The user may also need to adjust parameters we have already estimated (such as FPGA Vcco values) where appropriate. All values are shown in milliwatts (mW).

| COMPONENT(S) | 1.0V | 1.5V | 1.8V | 3.3V |

|---|---|---|---|---|

| 200 MHz, Misc | 250 | |||

| USB | 500 | |||

| DDR3 | 730 | |||

| FPGA Vccint, Vccbram | ||||

| FPGA Vccaux | ||||

| FPGA Vcco15,16 (DDR3), est. | 280 | |||

| FPGA Vcco14 (USB), est. | 60 | |||

| FPGA Vcco (User I/O) | ||||

| Total (mW) | ||||

| Available (mW) | 3,000 | 2,250 | 2,700 | 4,950 |

Example XEM7320-A200 FPGA Power Consumption

Xilinx Power Estimator version 2015.3 was used to compute the following power estimates for the Vccint supply. These are simply estimates; your design requirements may vary considerably. The numbers below indicate approximately 80% utilization.

| COMPONENT | PARAMETERS | VCCINT | VCCAUX |

|---|---|---|---|

| Clock | 150 MHz GCLK, 220,000 fanout | 570 mW | |

| Logic (DFF) | 150 MHz, 220,000 DFFs | 550 mW | |

| Logic (LUT) | 150 MHz, 100,000 | 550 mW | |

| BRAM | 36-bit, 300 @ 150 MHz | 450 mW | |

| DSP | 150 MHz, 630 slices | 300 mW | |

| Misc. | DCM, PLL, etc. | 10 mW | 500 mW |

| Total | 2,430 mW | 500 mW | |

| Available | 3,000 mW | 2,700 mW |